# amateurreihe

# electronica

Barthold/Bäurich

Mikroprozessoren –

Mikroelektronische

Schaltkreise und ihre

Anwendung (Teil 1)

222/

223

electronica · Band 222/223

HANS BARTHOLD

DR. HEINZ BÄURICH

# **Mikroprozessoren- Mikroelektronische Schaltkreise und ihre Anwendung**

Teil 1:

Grundlagen der Mikrorechentechnik

**MILITÄRVERLAG

DER DEUTSCHEN DEMOKRATISCHEN

REPUBLIK**

**Barthold , H.; Dr. Bäurich, H.:**

**Mikroprozessoren – Mikroelektronische Schaltkreise und ihre Anwendung.**

Teil 1: Grundlagen der Mikrorechentechnik. –

3., überarbeitete Aufl., – Berlin:

Militärverlag der DDR (VEB), 1985. –

184 S.: 108 Bilder – (electronica: 222/223

**3. Auflage, 1985**

© Militärverlag der

Deutschen Demokratischen Republik (VEB) – Berlin, 1980

Lizenz-Nr. 5

Printed in the German Democratic Republic

Gesamtherstellung: Druckerei Märkische Volksstimme Potsdam

Lektor: Steffen Würtenberger

Zeichnungen: Johanna Goernemann

Typografie: Martina Schwarz

Redaktionsschluß: 20. September 1984

LSV 3539

Bestellnummer: 746 692 4

00380

# Inhaltsverzeichnis

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| <b>Vorwort</b>                                                                  | 6  |

| <b>1. Erläuterungen zu den Abkürzungen</b>                                      | 8  |

| 1.1. Aufstellung häufig verwendeter Formelzeichen und Abkürzungen               | 8  |

| 1.2. Wertzuweisung bei logischen Signalen                                       | 8  |

| <b>2. Grundlagen der Rechentechnik</b>                                          | 9  |

| 2.1. Aufbau eines Rechners                                                      | 9  |

| 2.1.1. Speicher                                                                 | 10 |

| 2.1.2. Rechenwerk                                                               | 11 |

| 2.1.3. Steuerwerk                                                               | 12 |

| 2.2. Darstellung von Daten                                                      | 14 |

| 2.2.1. Zahlendarstellung                                                        | 14 |

| 2.2.1.1. Ganze Zahlen im Dualsystem                                             | 14 |

| 2.2.1.2. Gebrochene Zahlen im Dualsystem                                        | 16 |

| 2.2.1.3. Darstellung von negativen Zahlen                                       | 17 |

| 2.2.1.4. Mathematische Formulierung der Komplementbildung                       | 18 |

| 2.2.1.5. Zahlensysteme mit der Basis 8 (Oktalsystem) und 16 (Hexadezimalsystem) | 19 |

| 2.2.1.6. Ziffernkode                                                            | 19 |

| 2.2.1.7. Zahlenbereich im Rechner                                               | 22 |

| 2.2.2. Darstellung von Text (Zeichencode)                                       | 23 |

| 2.2.3. Rechnen mit Dualzahlen                                                   | 24 |

| 2.3. Aufbau der Befehle                                                         | 31 |

| 2.4. Befehlsschlüssel eines Rechners                                            | 32 |

| 2.5. Befehlsabarbeitung                                                         | 34 |

| 2.6. Ein- und Ausgabesteuerung (E/A-Steuerung)                                  | 36 |

| 2.6.1. Prinzip der E/A-Steuerung                                                | 36 |

| 2.6.2. Programmierte Ein- und Ausgabe                                           | 38 |

| 2.6.3. Autonome Ein- und Ausgabe                                                | 38 |

| 2.7. Programmunterbrechung (INTERRUPT)                                          | 41 |

| 2.8. STACK-Organisation                                                         | 42 |

|           |                                                                                  |            |

|-----------|----------------------------------------------------------------------------------|------------|

| 2.9.      | Zusammenstellung der Funktionseinheiten eines Rechners . . . . .                 | 43         |

| <b>3.</b> | <b>Aufbau und Arbeitsweise digitaler Schaltkreise für Mikrorechner . . . . .</b> | <b>44</b>  |

| 3.1.      | Übersicht . . . . .                                                              | 44         |

| 3.2.      | Schaltalgebra . . . . .                                                          | 45         |

| 3.3.      | Logische Grundschaltkreise . . . . .                                             | 52         |

| 3.4.      | Informationsspeicherung . . . . .                                                | 53         |

| 3.4.1.    | Überblick . . . . .                                                              | 53         |

| 3.4.2.    | Register . . . . .                                                               | 54         |

| 3.4.3.    | Speicher . . . . .                                                               | 61         |

| 3.4.4.    | Zusammenstellung einiger Speicherschaltkreise . . . . .                          | 76         |

| 3.5.      | Codier- und Decodierschaltungen . . . . .                                        | 82         |

| 3.6.      | Rechenschaltkreise . . . . .                                                     | 94         |

| 3.7.      | Bustreiber . . . . .                                                             | 100        |

| 3.8.      | Zähler . . . . .                                                                 | 103        |

| 3.9.      | Taktgeneratoren . . . . .                                                        | 107        |

| <b>4.</b> | <b>Mikroprozessoren . . . . .</b>                                                | <b>110</b> |

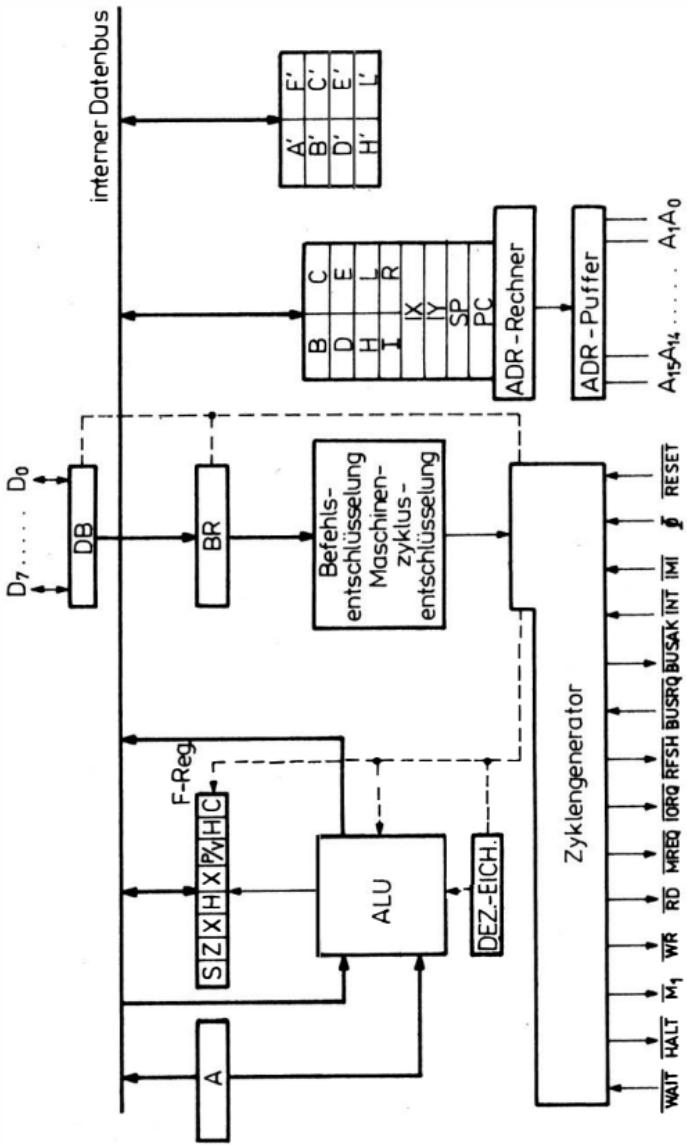

| 4.1.      | Der Mikroprozessorbaustein <i>U 880</i> . . . . .                                | 111        |

| 4.1.1.    | Registerstruktur des Mikroprozessorbausteins <i>U 880</i> . . . . .              | 112        |

| 4.1.2.    | Befehlsaufbau des Bausteins <i>U 880</i> . . . . .                               | 115        |

| 4.1.2.1.  | Befehlsstruktur . . . . .                                                        | 115        |

| 4.1.2.2.  | Adreßbildung . . . . .                                                           | 116        |

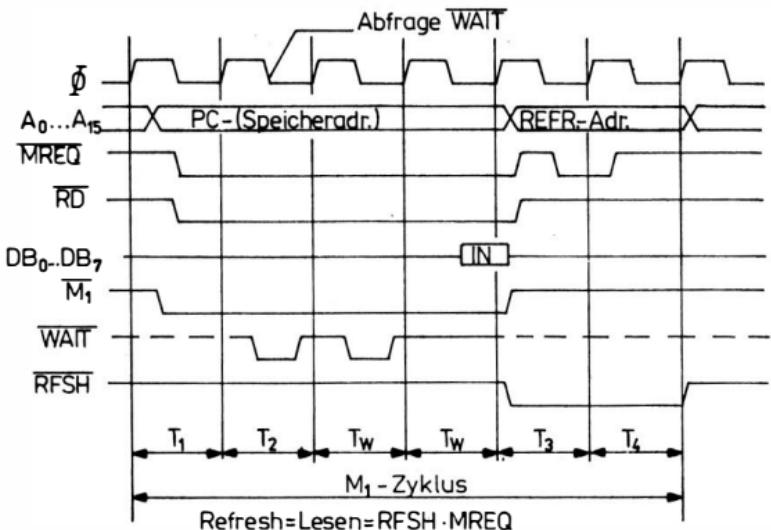

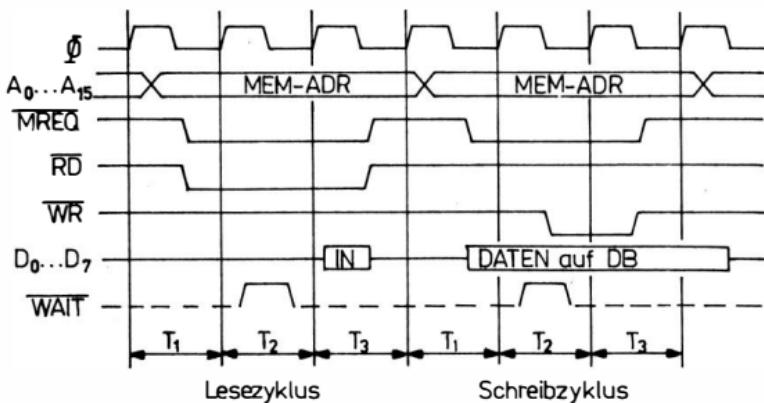

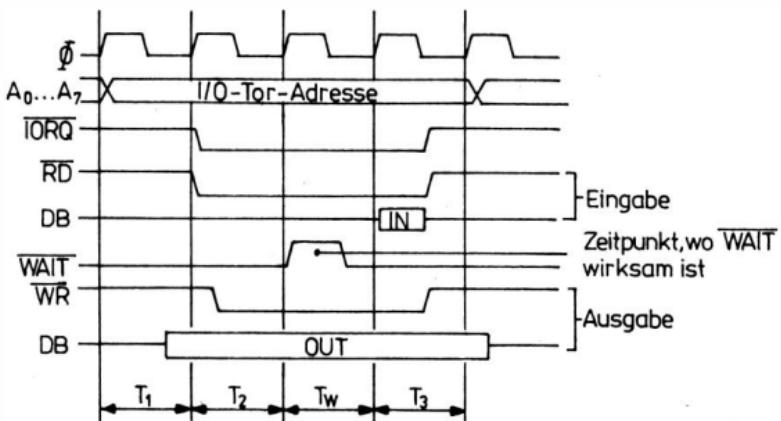

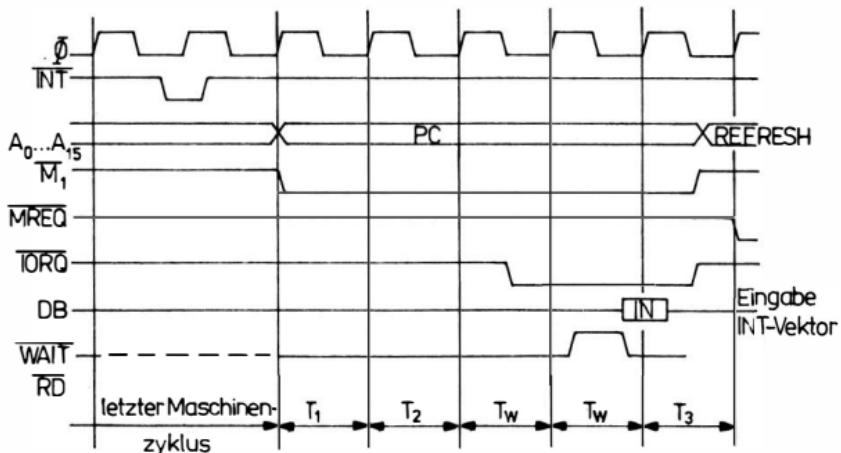

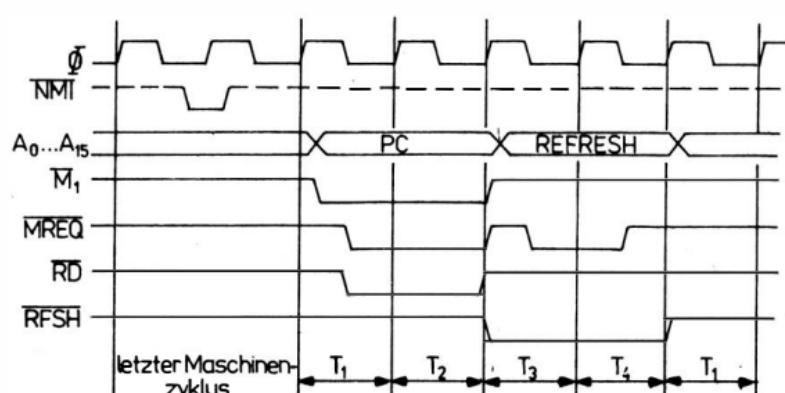

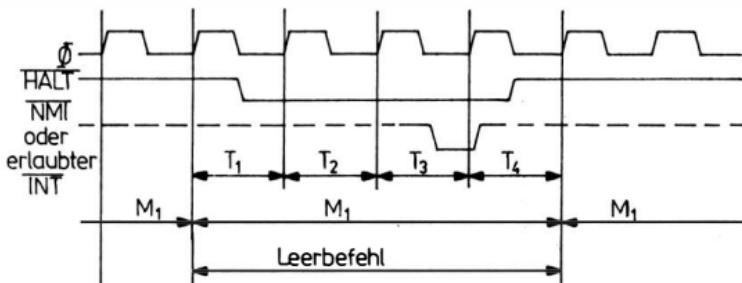

| 4.1.3.    | Zeitverhalten . . . . .                                                          | 117        |

| 4.1.4.    | Befehlsabarbeitung . . . . .                                                     | 123        |

| 4.1.5.    | Befehlsliste des Prozessors <i>U 880</i> . . . . .                               | 124        |

| 4.1.5.1.  | Verwendete Abkürzungen bei der Befehlsbeschreibung . . . . .                     | 124        |

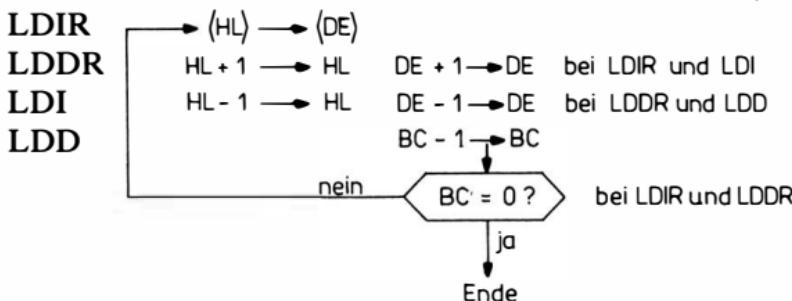

| 4.1.5.2.  | Transportbefehle . . . . .                                                       | 125        |

| 4.1.5.3.  | Rechen- und logische Operationen mit einem Operand . . . . .                     | 132        |

| 4.1.5.4.  | Rechen- und logische Operationen mit zwei Operanden . . . . .                    | 139        |

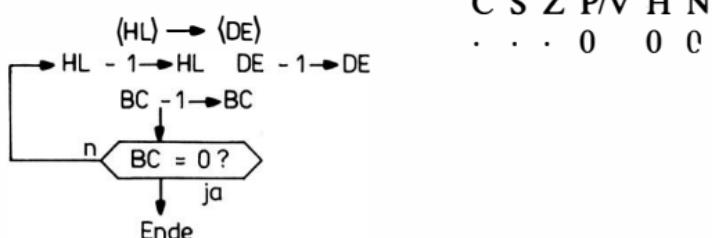

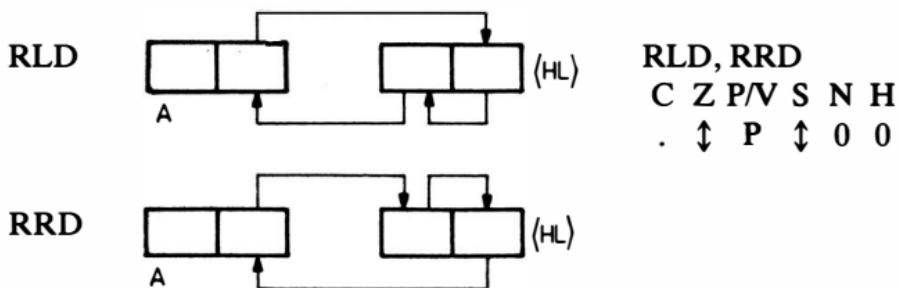

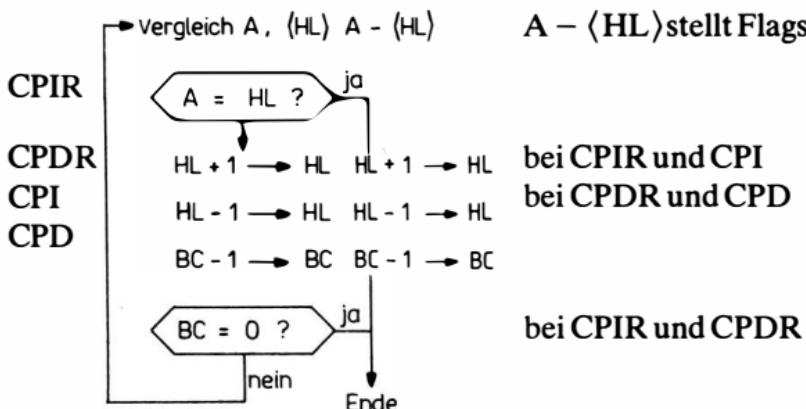

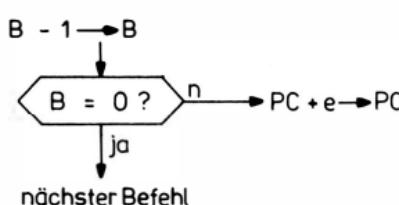

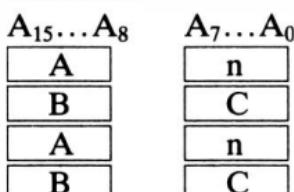

| 4.1.5.5.  | Rechen- und logische Operationen mit mehreren Operanden . . . . .                | 142        |

| 4.1.5.6.  | Sprungbefehle . . . . .                                                          | 144        |

| 4.1.5.7.  | Unterprogrammbefehle . . . . .                                                   | 146        |

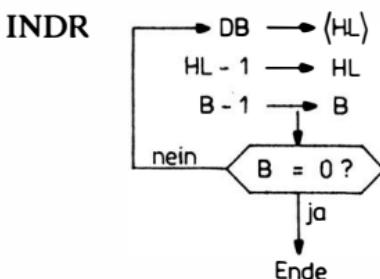

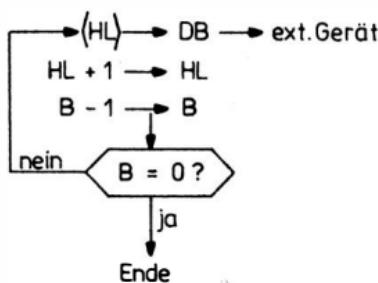

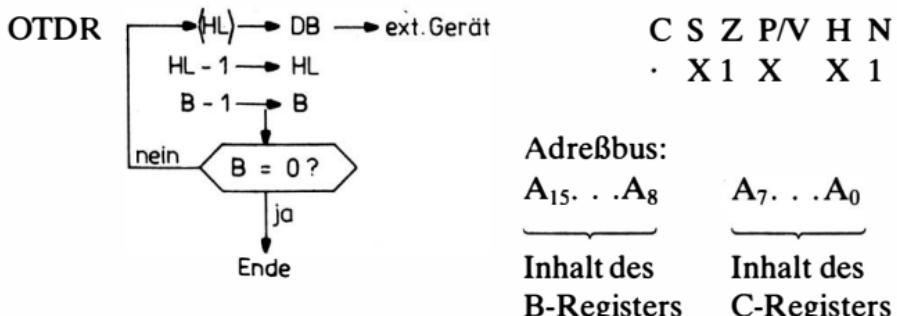

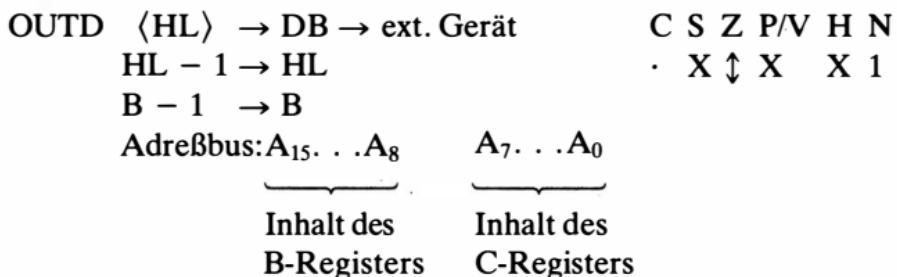

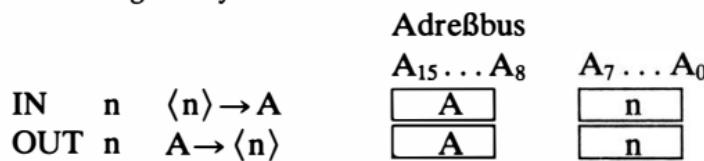

| 4.1.5.8.  | Ein- und Ausgabebefehle . . . . .                                                | 148        |

|          |                                                         |     |

|----------|---------------------------------------------------------|-----|

| 4.1.5.9. | Steuerbefehle                                           | 153 |

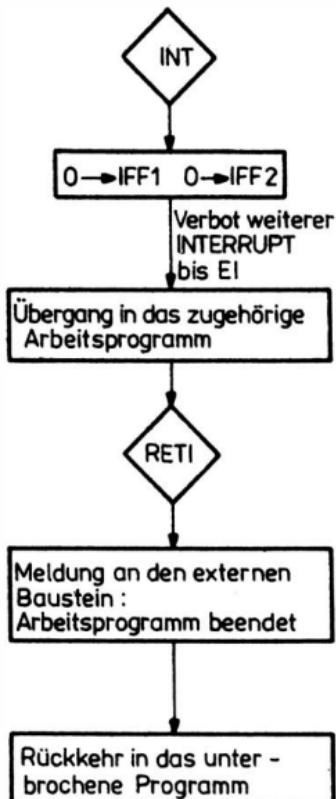

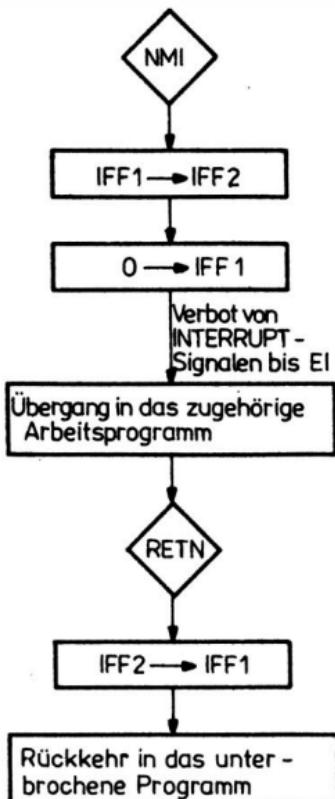

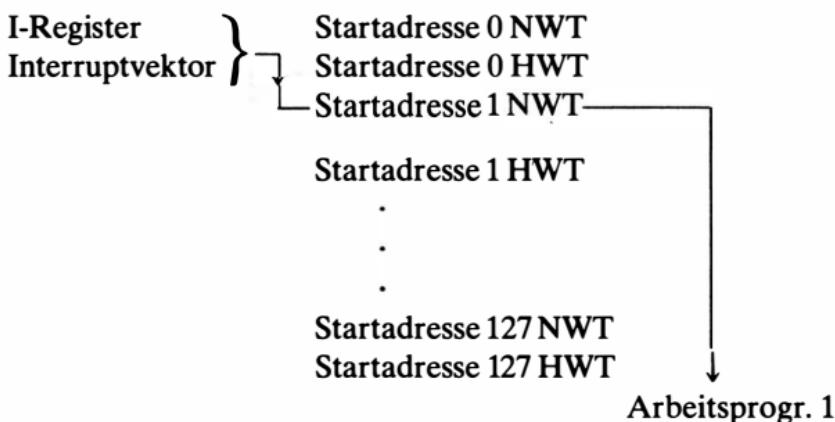

| 4.1.6.   | INTERRUPT                                               | 153 |

| 4.1.7.   | Starten des Prozessors <i>U 880</i>                     | 157 |

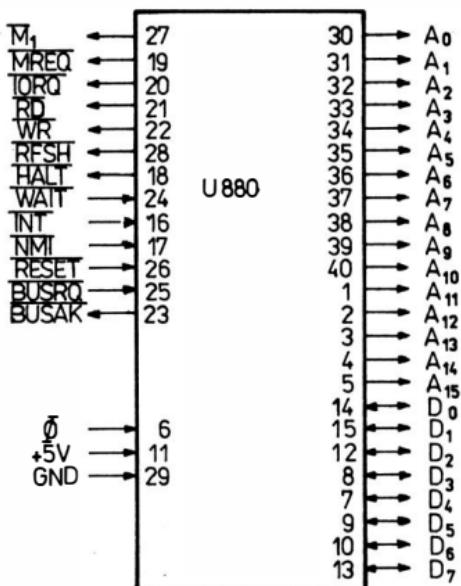

| 4.1.8.   | Anschlüsse an den Baustein <i>U 880</i>                 | 157 |

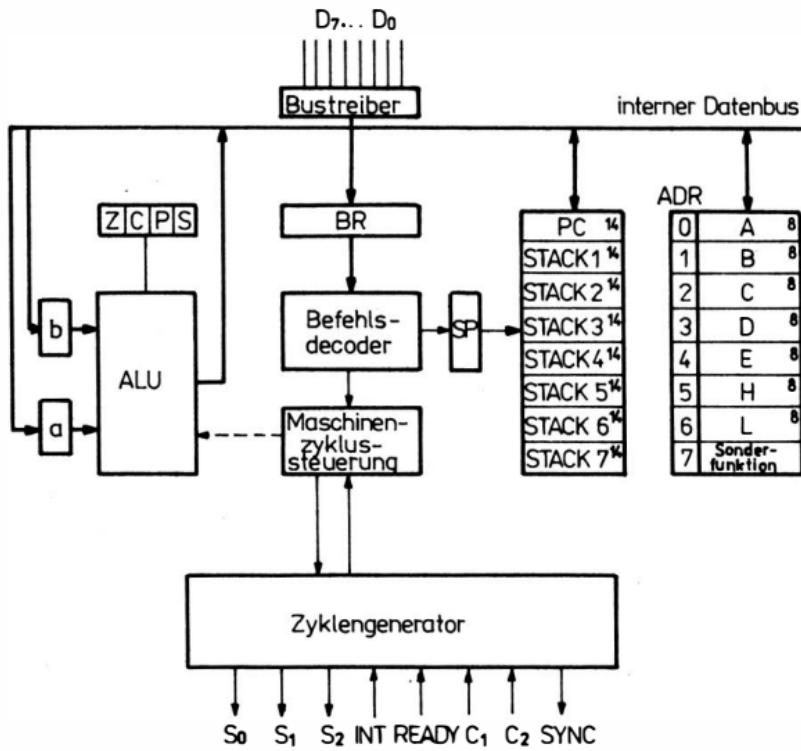

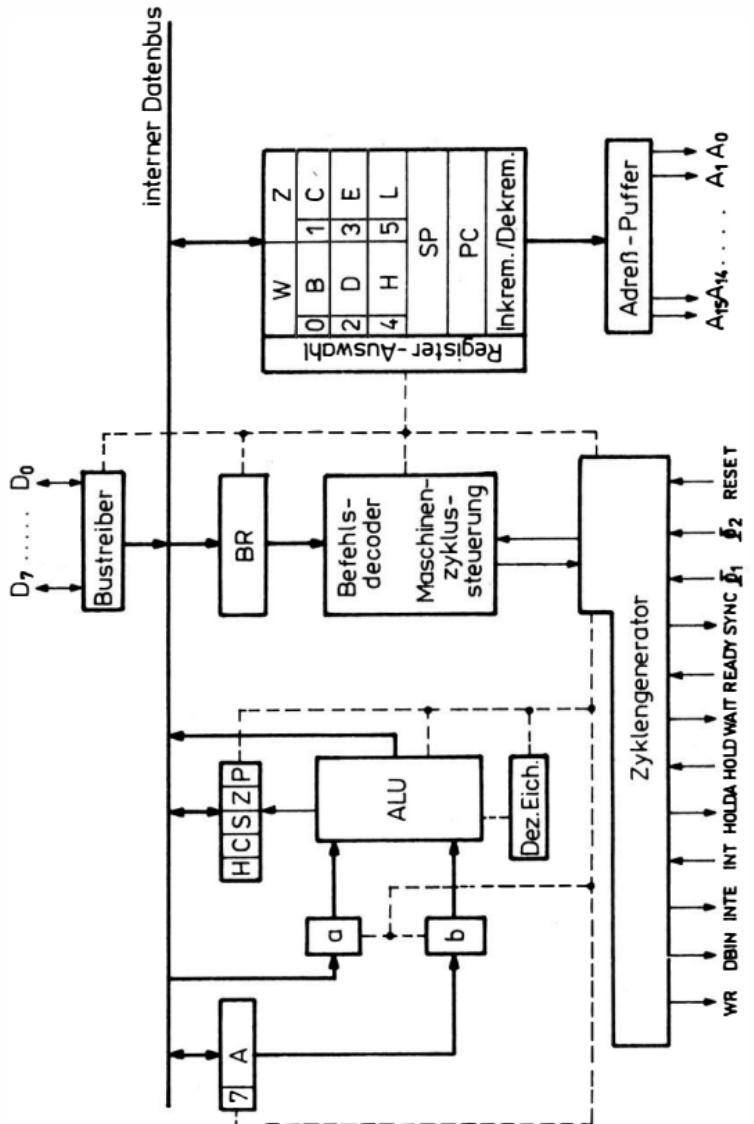

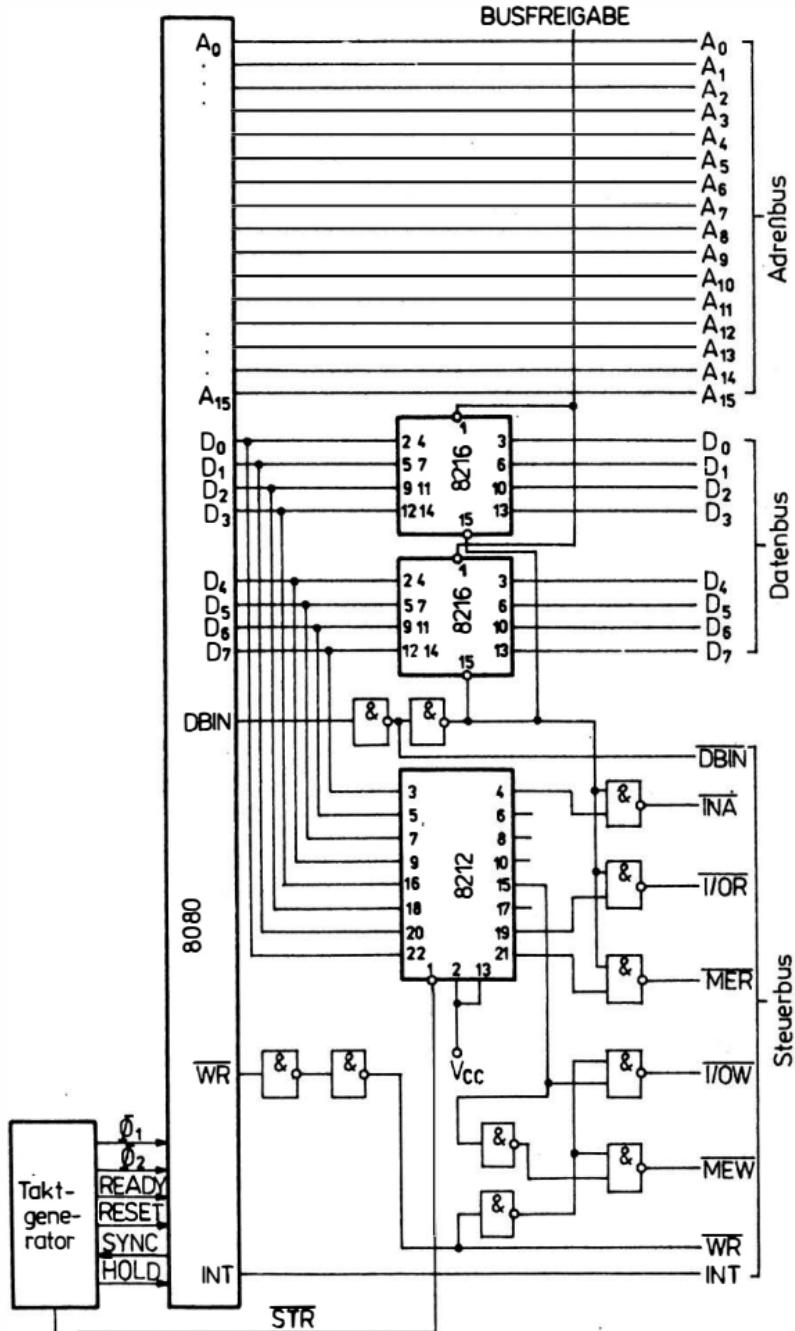

| 4.2.     | Der Mikroprozessorbaustein <i>8080</i>                  | 160 |

| 4.2.1.   | Registerstruktur                                        | 160 |

| 4.2.2.   | Befehlsaufbau                                           | 160 |

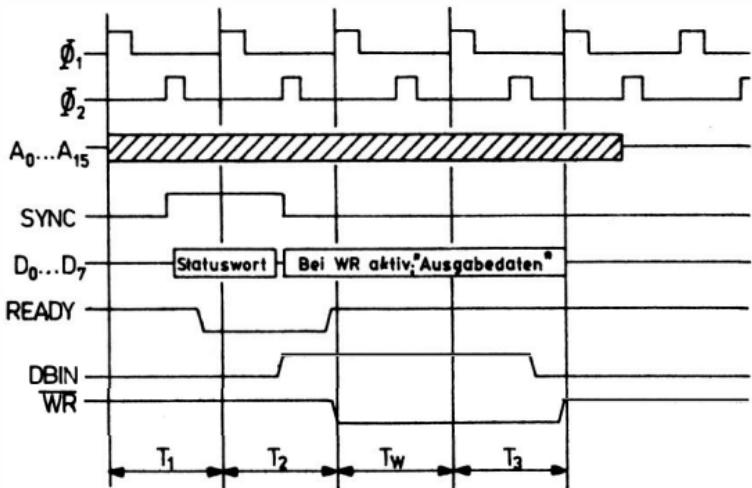

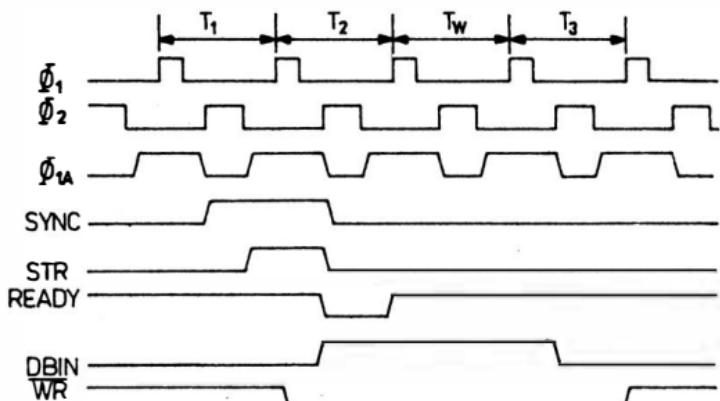

| 4.2.3.   | Zeitverhalten                                           | 161 |

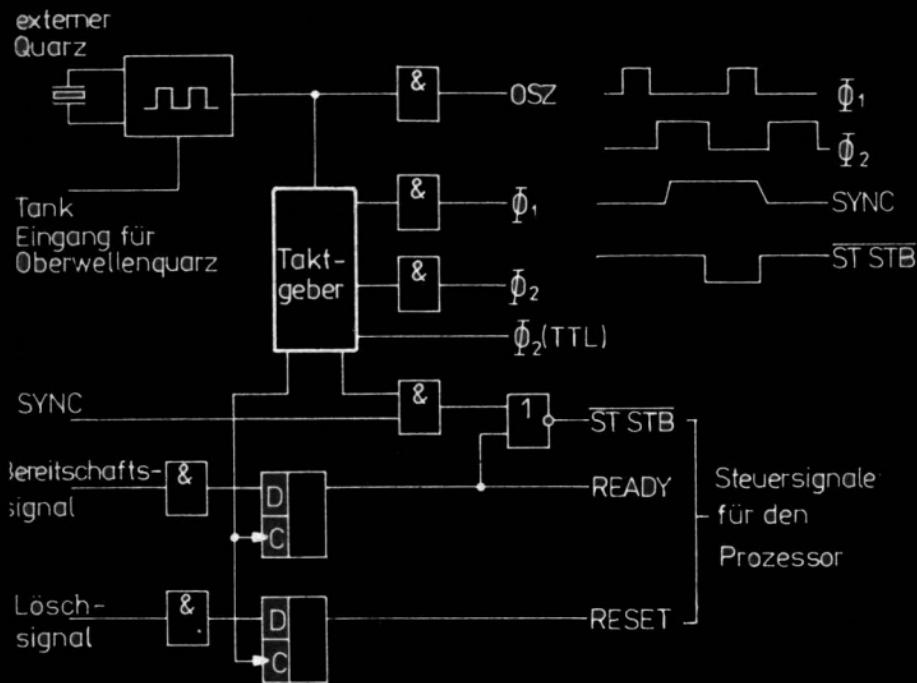

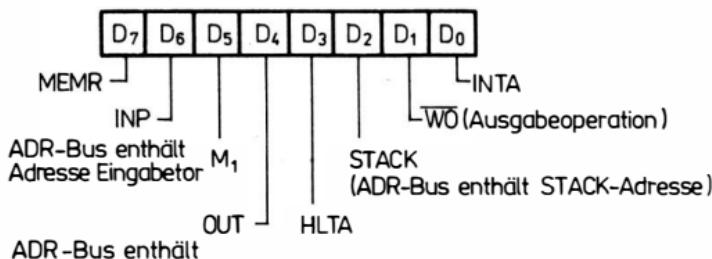

| 4.2.4.   | Anschlußsignale                                         | 163 |

| 4.2.5.   | Anschluß von Schaltkreisen an den Prozessor <i>8080</i> | 165 |

| 4.2.6.   | Befehlsschlüssel des Prozessors <i>8080</i>             | 167 |

| 4.2.7.   | Programmunterbrechung                                   | 167 |

## **Anhang**

|                                                              |     |

|--------------------------------------------------------------|-----|

| Befehlstabellen der Prozessoren <i>U 880</i> und <i>8080</i> | 168 |

| Codierungstabelle <i>U 880</i>                               | 178 |

## **Vorwort**

Der Mikroprozessor ist sehr schnell zu einem Begriff geworden, der aus der Elektronik nicht mehr wegzudenken ist. In der Fachliteratur spricht man in diesem Zusammenhang von Bausteinen der künftigen Automatisierungstechnik. Selbst solche Aussagen wie „Nervensystem der Technik“ werden im Zusammenhang mit dem Mikroprozessor gebraucht. Unsere Massenmedien berichten in Wort und Bild, daß durch den Mikroprozessor ein Teil der Arbeitswelt völlig verändert wird. Während in den kapitalistischen Ländern die Rationalisierung mit Hilfe dieser Elektronik dazu führt, daß Arbeitsplätze abgeschafft werden und dadurch die Arbeitslosigkeit weiter steigt, dient der Einsatz der Mikrorechentechnik in den sozialistischen Ländern zum Nutzen der gesamten Gesellschaft und somit dem Wohl jedes einzelnen.

Aus allen diesen Informationen heraus drängen sich die Fragen auf, was ist ein Mikroprozessor, was kann er wirklich leisten? Das gesamte Gebiete der Elektronik hat sich seit 1945 sehr rasch entwickelt. Eine wesentliche Rolle dabei spielt die Entwicklung der Bauelemente. Von den anfänglichen Bauelementen der Informationstechnik bis zu den hochintegrierten Schaltkreisen haben sich Platz- und Energiebedarf für ein aktives Bauelement sehr stark verringert, gleichzeitig sind Zuverlässigkeit und Betriebssicherheit in sehr hohem Maße angestiegen.

Alle Gebiete der Elektronik wurden von dieser schnellen Bauelementeentwicklung beeinflußt. Dabei ist auf dem Gebiet der elektronischen Rechentechnik diese Entwicklung besonders sichtbar. Aus diesem Fachgebiet kommen auch die programmierbaren Schaltkreise, wobei der bekannteste Vertreter der Mikroprozessor ist. Er stellt den eigentlichen Rechenschaltkreis dar; mit ihm lassen sich alle Verknüpfungen von Zahlen und logischen Größen realisieren.

Die Verknüpfung solcher Größen bildet gleichzeitig die Grundlage der Automatisierungstechnik. Im Grunde genommen können mit jedem elektronischen Rechner die Probleme der Automatisierung gelöst werden. Aber erst durch die Möglichkeit, den Rechner als Bauelement (Chip) herzustellen, wurde die stürmische Entwick-

lung in der Automatisierungstechnik erreicht. Es läßt sich einschätzen, daß diese Entwicklung noch am Anfang steht. Aber schon in den nächsten Jahren wird der Mikroprozessor in vielen technischen Geräten eine Selbstverständlichkeit sein.

Auf Grund der großen Nachfrage erscheinen die Hefte „Mikroprozessoren – Mikroelektronische Schaltkreise und ihre Anwendung“ in einer überarbeiteten Form als zwei Doppelhefte. Sie sind als Einheit zu betrachten. Bei der Überarbeitung wurde das Kapitel über den Mikroprozessor *U 808* herausgenommen, da er für Neuentwicklungen nicht mehr eingesetzt wird. Hinzugekommen sind ein Kapitel über die Assemblersprache MAPS-K 1520 sowie ein Kapitel mit Programmbeispielen zum *U 880*.

# **1. Erläuterungen zu den Abkürzungen**

## **1.1. Aufstellung häufig verwendeter Formelzeichen und Abkürzungen**

|                      |                                                                |

|----------------------|----------------------------------------------------------------|

| <i>B</i>             | Zahlenbasis                                                    |

| <i>E</i>             | Exponent einer Gleitkommazahl                                  |

| <i>H</i>             | hoher logischer Spannungspegel                                 |

| <i>L</i>             | niedriger logischer Spannungspegel                             |

| <i>m</i>             | Mantisse einer Gleitkommazahl                                  |

| <i>P<sub>j</sub></i> | Elementarkonjunktion, die der Dualzahl <i>j</i> zugeordnet ist |

| <i>T</i>             | logischer Term (logischer Ausdruck)                            |

| <i>Q</i> , <i>Q̄</i> | Ausgänge eines Flip-Flop                                       |

| <i>V</i>             | Vorzeichen einer Zahl                                          |

| <i>X<sub>i</sub></i> | Ziffern einer Zahl                                             |

| <i>X(Y)</i>          | Wert einer Zahl                                                |

| <i>X'</i>            | Zweierkomplement der Zahl X                                    |

## **1.2. Wertzuweisung bei logischen Signalen**

In den verwendeten Schaltbildern sind die logischen Signale durch Abkürzungen eingezeichnet. Die Abkürzungen werden im Text erläutert. Ist am Eingang oder am Ausgang eines Bausteins ein logisches Signal S durch S gekennzeichnet, heißt das: Das Signal hat Hochpegel, wenn dem Signal der logische Wert 1 zugeordnet ist. Wird es durch  $\bar{S}$  gekennzeichnet, heißt das: Das Signal hat Tiefpegel, wenn dem Signal der logische Wert 1 zugeordnet ist. In den Funktionstabellen bedeuten die Bezeichnungen H bzw. L hoher bzw. niedriger Spannungspegel. Dagegen kennzeichnen 1 oder 0 die den Eingängen bzw. Ausgängen zugeordneten logischen Werte. Die Bezeichnung H und L wurde in den Fällen gewählt, wo es sich um die Beschreibung der Signalpegel in einer Schaltung handelt. 0 und 1 stehen in den Fällen, wo aus vorgegebenen logischen Bedingungen das logische Schaltbild entworfen wird, ohne daß dabei die Signalzuordnung H oder L erforderlich ist.

## **2. Grundlagen der Rechentechnik**

### **2.1. Aufbau eines Rechners**

Der Rechner war das Vorbild für die Entwicklung der Mikroprozessoren. Viele Vorgänge in Natur und Technik laufen nach mathematischen oder logischen Regeln ab. Der Rechner ist die Basis zur Nachbildung solcher Vorgänge. Durch die Möglichkeit, ihn zu programmieren, kann man in ihm Algorithmen speichern und zu jeder Zeit abarbeiten lassen.

Der Rechner ist ein universelles Hilfsmittel zur Realisierung von Steuerungen, zur Nachbildung von Modellen sowie zur Lösung von mathematischen Aufgaben, für die man sich bisher umfangreicher elektronischer Schaltungen bedienen mußte (z. B. Digitaluhr, Digitalvoltmeter, Zähler). Durch seine Programmierbarkeit hat er gegenüber anderen Lösungen den Vorteil, daß er sich ohne Änderung der *Hardware* (fest verdrahtete Schaltung) an das jeweilige Programm anpassen läßt. Sein Einsatz für eine bestimmte Lösung hängt im Prinzip nur vom Kostenverhältnis zwischen Rechner und konkreter Schaltungstechnik ab.

Ein Rechner soll eine Aufgabe nach einer Lösungsvorschrift abarbeiten. Dabei ist der Ablauf derselbe wie bei einer Handrechnung. Entsprechend der Lösungsvorschrift, die aus einer Reihe von Anweisungen besteht, werden die Daten durch Rechenoperationen miteinander verknüpft, eventuelle Zwischenergebnisse notiert und die Ergebnisse auf einem gesonderten Formular zusammengefaßt.

In der gleichen Weise arbeitet ein Rechner. Die Lösungsvorschrift, die aus einer Reihe von Anweisungen (*Befehlen*) besteht, ist das *Programm*. Man muß es, damit es abgearbeitet werden kann, in einen Speicher eingeben. Ebenso müssen die Ausgangsdaten, die Zwischenwerte sowie die Resultate gespeichert werden. Das *Rechenwerk*, das im wesentlichen die 4 Grundrechenarten Addition, Subtraktion, Multiplikation und Division sowie die logischen Operationen UND, ODER und NEGATION ausführt, verknüpft die Daten. Für die Steuerung des gesamten Ablaufs gibt es ein *Steuerwerk*. Dieses Steuerwerk liest Anweisung für Anweisung der

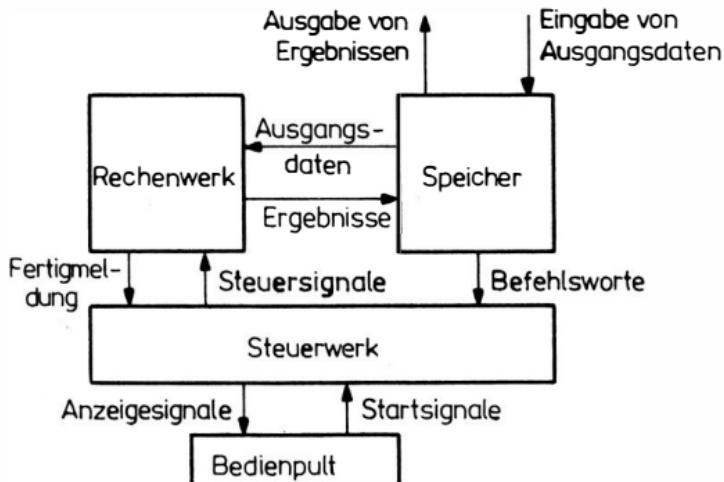

Bild 2.1 Grundsätzliche Struktur eines Rechners

Lösungsvorschrift aus dem Speicher und gibt dem Rechenwerk Signale zur Ausführung der in der Anweisung vorgegebenen Funktion. Rechenwerk und Steuerwerk bilden die CPU (Central Processor Unit). Ein Rechner besteht also aus den Hauptbestandteilen Speicher, Rechenwerk und Steuerwerk.

Außerdem gehören zum Rechner noch Ein- und Ausgabegeräte zur Eingabe des Programms und der Ausgangsdaten einer Aufgabe sowie zur Ausgabe der Ergebnisse. Ferner ist an jedem Rechner ein Bedienpult angeschlossen, über das bestimmte Funktionen (Starten eines Programms, Ein- und Ausschalten von Teilgeräten, Sichtanzeigen) gesteuert werden können.

Bild 2.1 zeigt die grundsätzliche Struktur eines solchen Rechners.

### 2.1.1. Speicher

Der Speicher hat die Aufgabe, alle Informationen, die zur Lösung einer Aufgabe benötigt werden, zu speichern.

Dazu gehören das Programm, das aus einer Folge von Befehlen besteht, die Ausgangsdaten, die Zwischenresultate und die Endergebnisse.

Ausgangsdaten, Zwischenresultate und Endergebnisse sind im allgemeinen Zahlen oder alphanumerische Zeichen (Text). Zur Darstellung einer Zahl oder eines Befehls dient innerhalb des Rechners ein sogenanntes *Maschinenwort*, das aus einer Bit-Folge

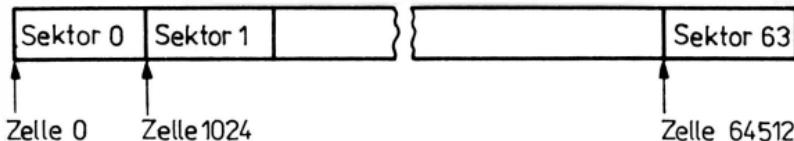

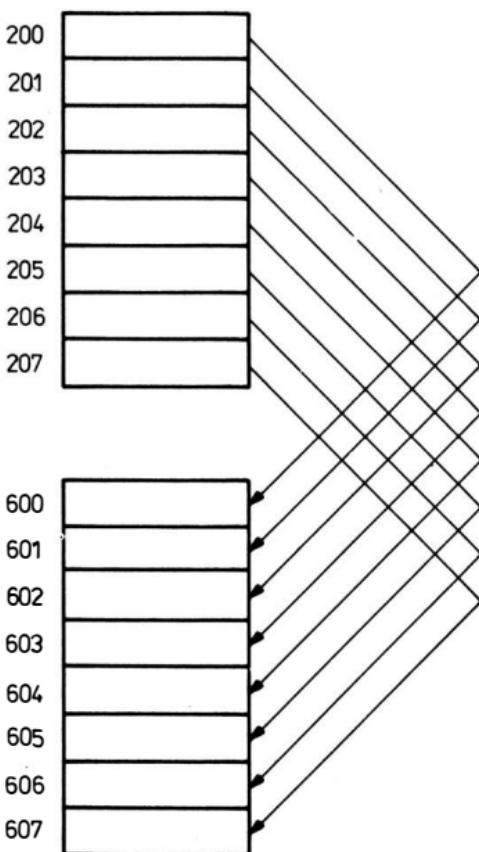

Bild 2.2 Logische Aufteilung eines 64-K-Speichers in 64 Sektoren

besteht. Es hat eine vorgegebene Wortlänge. Den Platz, der notwendig ist, um ein solches Wort im Rechner zu speichern, nennt man eine *Speicherzelle*. Der Speicher besteht aus einer größeren Anzahl solcher Speicherzellen, die durchnumeriert sind. Die Nummer der Speicherzelle nennt man die *Adresse*.

In der Rechentechnik ist die Mengenangabe Kilo (Kilobyte oder Kiloworte) üblich. Ein Kilo kennzeichnet hier jedoch nicht die tausendfache Menge, sondern das 1024fache (1 Kbyte = 1024 Byte), da die Kapazität eines Speichers fast immer einer Zweierpotenz entspricht. Zu einer solchen Speicherplatzanzahl ist eine optimale Adressentschlüsselung möglich. Manchmal wird der Speicher in Seiten oder Sektoren aufgeteilt. Entsprechend unterteilt sich dann auch die Adresse in Seitenadresse (Sektoradresse) und Zellenummer innerhalb der Seite (Sektor). Bild 2.2. zeigt die Aufteilung eines Speichers mit 64K-Zellen in 64 Sektoren.

Technisch werden Speicher meistens als Ferritkernspeicher oder Halbleiter ausgeführt (s. Abschnitt 3.4.3.).

### 2.1.2. Rechenwerk

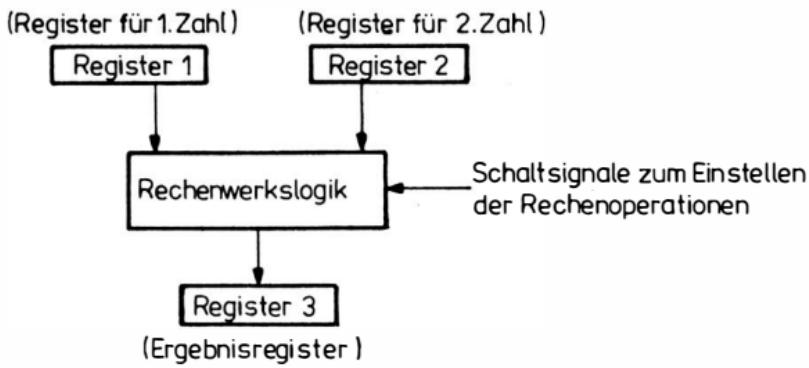

Das Rechenwerk dient zur Ausführung von Rechenoperationen. Es bekommt durch das Steuerwerk eine Folge von Schaltsignalen, die es auf die gerade auszuführenden Rechenoperationen umschalten. Vom Speicher erhält es die Zahlen, die zur Ausführung der Rechenoperationen notwendig sind.

Die Zahlen werden im Rechenwerk zwischengespeichert. Dazu hat das Rechenwerk mehrere Register, in denen die Ausgangsdaten einer Rechenoperation gespeichert sind.

Nach der Ausführung der Rechenoperation wird das Ergebnis ebenfalls in einem Register gespeichert. Bild 2.3. zeigt das Grundprinzip eines Rechenwerks.

Bild 2.3 Grundprinzip eines Rechenwerks

Zu den Operationen, die ein Rechenwerk eines Rechners ausführt, gehören:

- Arithmetische Rechenoperationen für die im Rechner verdrahteten Zahlendarstellungen (**ADDITION**, **SUBTRAKTION**, **MULTIPLIKATION** und **DIVISION**). Bei Mikrorechnern sind im allgemeinen nur Addition und Subtraktion möglich. Multiplikation und Division müssen programmiert werden.

- Logische Operationen (**UND**, **ODER**, **EXKLUSIV-ODER**, **NEGATION**, **VERSCHIEBUNG**)

- Zahlenumwandlungen.

Das Rechenwerk eines Mikrorechners wird im allgemeinen als *arithmetisch-logische Einheit* (ALU – *arithmetic-logic unit*) bezeichnet. Die ALU ist eine Logikschaltung, die durch Steuersignale so eingestellt werden kann, daß ein oder zwei Eingangsbitmuster entsprechend der eingestellten Operation verarbeitet werden.

### 2.1.3. Steuerwerk

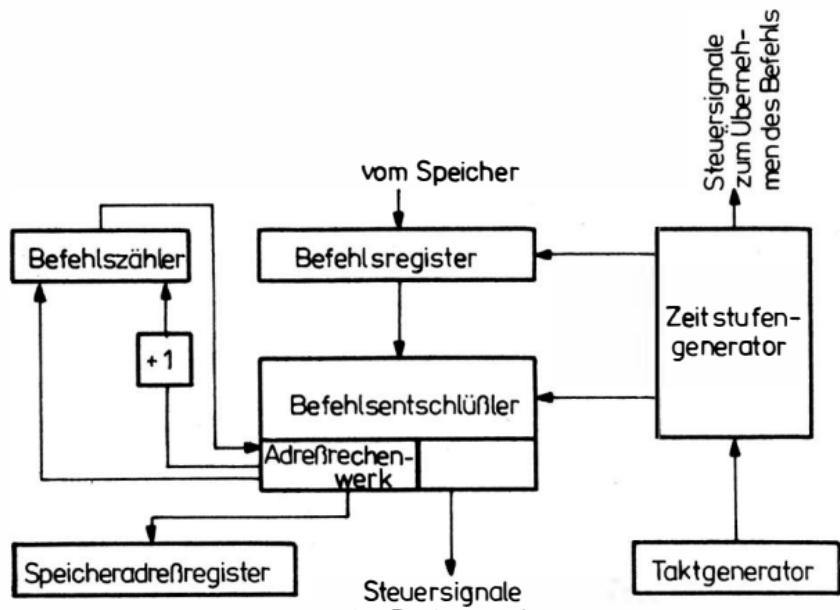

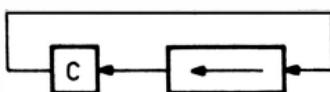

Das Steuerwerk übernimmt die Befehle eines Programms in der vorgegebenen Reihenfolge aus dem Speicher, entschlüsselt sie und bildet daraus die Steuersignale für das Rechenwerk. Bild 2.4 zeigt den logischen Aufbau des Steuerwerks.

Der Befehlszähler enthält die Adresse des zu holenden Befehls. Der vom Speicher übernommene Befehl wird zur Befehlsentschlüsselung im Befehlsregister zwischengespeichert. Das Spei-

Bild 2.4 Aufbau des Steuerwerks eines Rechners

cheradreßregister enthält die Adresse des zum Befehl benötigten Operanden. (Mehrere Operanden [Zahlen] werden nacheinander aus dem Speicher geholt.)

Der Zeitstufengenerator erzeugt eine Reihe von Zeitsignalen, die den Ablauf der Befehlsabarbeitung festlegen. Den Grundtakt dazu liefert der Taktgenerator. Die wichtigsten Schritte einer Befehlsabarbeitung sind:

- Übernehmen des Befehls aus dem Speicher;

- Entschlüsseln des Befehls;

- Ermitteln der Operandenadresse;

- Holen der Operanden aus dem Speicher;

- Ausführung des Befehls;

- Ermittlung der Adresse des nächsten Befehls.

Da der Rechner aus Speicher, Rechen- und Steuerwerk besteht, ergibt sich die Möglichkeit, automatisch, d. h. programmgesteuert, beliebige Funktionen oder Aufgaben abzuarbeiten. Zu diesem Zweck enthält jede Aufgabe 2 Teilinformationen. Die erste Teilinformation beinhaltet die Daten bzw. Zahlen, die verarbeitet werden sollen. Der zweite Teil der Information sind die Anweisungen (Befehle), die aussagen, wie die Daten verarbeitet werden sollen. Beide Teilinformationen gibt man über externe Geräte (Eingabetastatur, Schreibmaschine, Lochbandleser, Lochkarteneingabe

usw.) in den Speicher ein. Vom Speicher werden die Anweisungen in einer festgelegten Reihenfolge ins Steuerwerk übernommen, entschlüsselt und vom Rechenwerk abgearbeitet. Zwischen- und Endresultate gelangen in den Speicher zurück und können von dort aus wieder über externe Geräte (Anzeige, Schreibmaschine, Drucker) ausgegeben werden.

## 2.2. Darstellung von Daten

Da der Speicher aus einzelnen Zellen besteht, wobei jede Zelle eine Bit-Folge mit vorgegebener Länge speichern kann, müssen die zu verarbeitenden Daten (Zahlen) in Bit-Folgen umgewandelt werden. Dafür gibt es eine Reihe von Darstellungsarten. Je nach Länge einer Speicherplatzzelle und Anzahl der notwendigen Stellen für die Darstellung einer Zahl werden für die Speicherung einer Zahl eine oder mehrere Zellen benötigt. Das gleiche gilt für die Speicherung von alphanumerischem Text.

### 2.2.1. Zahlendarstellung

Ausgangspunkt für die Darstellung von Zahlen in Rechnern ist das *Dualsystem*. Dabei handelt es sich um ein Zahlensystem, das auf nur 2 Ziffern basiert (0 und 1). Zur Speicherung einer Dualziffer sind also nur 2 stabile Zustände notwendig, die sich leicht realisieren lassen.

#### 2.2.1.1. Ganze Zahlen im Dualsystem

Um eine Dezimalzahl in das Dualsystem zu übertragen, zerlegt man sie in Potenzen zur Basis 2, wobei jeder neuen Potenz von 2 eine neue Stelle zugeordnet wird.

##### *Beispiel*

Die Zahl 27 soll dual dargestellt werden. Aus Tabelle 2.1. ist zu erkennen, daß die größte in 27 enthaltene Zweierpotenz  $2^4 = 16$  ist, d. h., der Stellenwert  $2^4$  wird benötigt. Der Stellenwert  $2^3 = 8$  ergibt mit  $2^4$  zusammen 24, der Rest ist 3. Der Stellenwert  $2^2$  tritt also nicht, d. h. 0mal, auf, während die Stellenwerte  $2^1$  und  $2^0$  je einmal

**Tabelle 2.1.** Tabelle der Zweierpotenzen

| $2^n$ | $n$ | $2^{-n}$   |

|-------|-----|------------|

| 1     | 0   | 1          |

| 2     | 1   | 0,5        |

| 4     | 2   | 0,25       |

| 8     | 3   | 0,125      |

| 16    | 4   | 0,0625     |

| 32    | 5   | 0,03125    |

| 64    | 6   | 0,015625   |

| 128   | 7   | 0,0078125  |

| 256   | 8   | 0,00390625 |

erforderlich sind. Die Zahl 27 stellt sich im Dualsystem also folgendermaßen dar:

Stelle  $2^4$  Stelle  $2^3$  Stelle  $2^2$  Stelle  $2^1$  Stelle  $2^0$

|   |   |   |   |   |

|---|---|---|---|---|

| 1 | 1 | 0 | 1 | 1 |

|---|---|---|---|---|

Der Leser führe selbst die Umwandlung der folgenden Dezimalzahlen ins Dualsystem aus:

$$41 = 1 \cdot 2^5 + 0 \cdot 2^4 + 1 \cdot 2^3 + 0 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0 \triangleq 101001 \text{ (dual);}$$

$$15 = 1 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0 \triangleq 1111 \text{ (dual).}$$

### Umwandlung Dezimal → Dual

Eine weitere Methode besteht in der fortlaufenden Division durch 2.

#### Beispiel

Es soll die Dezimalzahl 93 durch fortlaufende Division durch 2 dual dargestellt werden.

| $2^6$              | $2^5$ | $2^4$ | $2^3$ | $2^2$ | $2^1$ | $2^0$ |

|--------------------|-------|-------|-------|-------|-------|-------|

| 93 : 2 = 46 Rest 1 |       |       |       |       |       | 1     |

| 46 : 2 = 23 Rest 0 |       |       |       |       |       | 0     |

| 23 : 2 = 11 Rest 1 |       |       |       |       |       | 1     |

| 11 : 2 = 5 Rest 1  |       |       |       |       |       | 1     |

| 5 : 2 = 2 Rest 1   |       |       |       |       |       | 1     |

| 2 : 2 = 1 Rest 0   |       |       |       |       |       | 0     |

| 1 : 2 = 0 Rest 1   |       |       |       |       |       | 1     |

|                    |       |       |       |       |       |       |

| 1                  | 0     | 1     | 1     | 1     | 0     | 1     |

$$93 \text{ (dezimal)} \triangleq 1011101 \text{ (dual).}$$

## **Umwandlung Dual → Dezimal**

Hier geht man von einem Rechenschema aus, in dem die 2er Potenzen wieder dezimal dargestellt werden.

*Beispiel*

$$10111 \triangleq 1 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0 \\ = 16 + 0 + 4 + 2 + 1 = 23.$$

### **2.2.1.2. Gebrochene Zahlen im Dualsystem**

Bei der Darstellung von Zahlen, die Stellen hinter dem Komma haben, wird ähnlich wie bei den ganzen Zahlen verfahren. Man benötigt dazu eine Tabelle der Potenzen von 2 mit negativen Exponenten. Zum Beispiel kann man die Zahl 0,625 folgendermaßen schreiben:

$$0,625 = 1 \cdot 2^{-1} + 0 \cdot 2^{-2} + 1 \cdot 2^{-3} \triangleq 0,101 \text{ (dual).}$$

Ein Dezimalbruch lässt sich ins Dualsystem durch fortlaufende Multiplikation mit der Grundzahl 2 überführen. Steht nach der Multiplikation mit 2 vor dem Komma eine 0, so ist die nächste Dualstelle eine 0. Steht eine 1 vor dem Komma, dann ist die nächste Dualstelle eine 1.

*Beispiel*

Umwandlung der Dezimalzahl 0,625

$$0,625 \cdot 2 = 1,250 \quad 1 \triangleq 1. \text{ Dualstelle nach dem Komma;}$$

$$0,25 \cdot 2 = 0,50 \quad 0 \triangleq 2. \text{ Dualstelle nach dem Komma;}$$

$$0,50 \cdot 2 = 1,00 \quad 1 \triangleq 3. \text{ Dualstelle nach dem Komma.}$$

Die Dezimalzahl 0,625 lautet dual 0,101. Die Begründung des Verfahrens liegt darin, daß bei jeder Multiplikation mit 2 die Zweierpotenzen um 1 erhöht werden und dabei die erste Ziffer vor dem Komma rückt. Diese Ziffer wird als Dualstelle übernommen.

Bei gemischten Zahlen wandelt man den ganzen Teil und den gebrochenen Teil – jeden für sich – in eine Dualzahl um.

*Beispiel*

Die Zahl 3,25 soll dual dargestellt werden. Die Zerlegung von 3,25 ergibt  $3 + 0,25$ . Der Zahl 3 entspricht die Dualzahl 11, der Zahl 0,25 entspricht die Dualzahl 0,01.

Damit lautet die Zahl 3,25 dual 11,01.

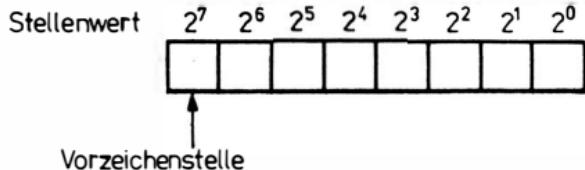

Bild 2.5

Darstellung von positiven und negativen ganzen Zahlen mit Hilfe von 8 Dualstellen

### 2.2.1.3. Darstellung von negativen Zahlen

In der Umgangssprache unterscheiden sich die negativen Zahlen von den positiven Zahlen durch ein negatives Vorzeichen. Für die Darstellung dieses Vorzeichens im Rechner kann man eine zusätzliche Dualstelle als Vorzeichenstelle einführen und z. B. folgende Vereinbarung treffen:

Vorzeichenstelle = 0 heißt positives Vorzeichen.

Vorzeichenstelle = 1 heißt negatives Vorzeichen.

Diese Darstellungsart wird in der Literatur mit „Betrag und Vorzeichen“ bezeichnet.

In den meisten Rechnern wird jedoch eine andere Darstellung, die *Komplementdarstellung*, verwendet, in der die negativen Zahlen in den positiven Zahlbereich transformiert werden. Der Vorteil besteht darin, daß sich die Subtraktion auf eine Addition zurückführen läßt.

In den meisten Mikroprozessoren stehen 8 Dualstellen (7 Dualstellen für die positiven Zahlen und eine Dualstelle für die Vorzeichenstelle) zur Verfügung (Bild 2.5). Werden diese 8 Dualstellen zur Darstellung ganzer Zahlen verwendet, so hat die Zahl +5 die Belegung in Zeile 1 von Bild 2.6. Die duale Darstellung der Zahl -5 mit Betrag und Vorzeichen ist aus Zeile 2 zu ersehen. Bei der Komplementdarstellung wird bei negativen Zahlen das Komplement zu  $2^8$  gebildet. Das heißt, im Rechner wird anstelle der Zahl

Stellenwert  $2^8 \quad 2^7 \quad 2^6 \quad 2^5 \quad 2^4 \quad 2^3 \quad 2^2 \quad 2^1 \quad 2^0$

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

+5

-5 (Betrag +Vorzeichen)

-5 (Zweierkomplement)

Vorzeichenstelle

Bild 2.6 Darstellung der Zahlen +5 und -5 im Zweierkomplement

$-x$  die Zahl  $2^8 - x$  gespeichert. Für die Zahl  $-5$  entsteht dabei die Belegung entsprechend Zeile 3 in Bild 2.6.

Für die Komplementbildung kann man folgende Regel aufstellen:

**Ausgehend von der positiven Dualzahl, werden zur Komplementbildung alle Stellen negiert und anschließend zum niedrigsten Stellenwert eine 1 addiert.**

#### **2.2.1.4. Mathematische Formulierung der Komplementbildung**

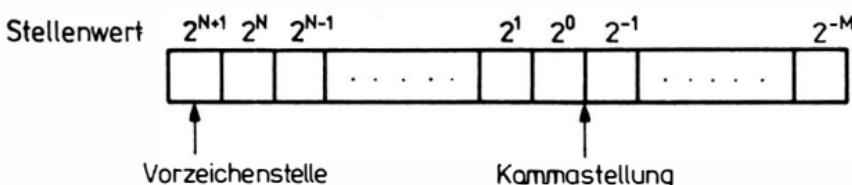

Der positive Zahlenbereich der nach Bild 2.7 dargestellten Zahlen ist

$$0 \leq x \leq \sum_{i=-M}^N 2^i = 2^{N+1} - 2^{-M}.$$

Da die negativen Zahlen in den positiven Zahlenbereich transformiert werden sollen, gilt für die Zahlen  $x'$  im Rechner:

$$x' = \begin{cases} x, & \text{falls } x \geq 0 \\ x + k, & \text{falls } x < 0 \end{cases}.$$

wobei  $k$  eine Komplementärzahl ist. Für die Komplementärzahl  $k$  ergeben sich folgende Bedingungen:

1. Es soll  $x' > 0$  sein.

2. Positive und negative Zahlen müssen unterscheidbar sein.

Damit muß für negative Zahlen  $x$

$$k + x \geq 2^{N+1} - 2^{-M}$$

sein, d. h.

$$k > 2^{N+1} - 2^{-M} - x = 2^{N+1} - 2^{-M} + |x|,$$

- und mit

$$|x|_{\max} = 2^{N+1} - 2^{-M}$$

wird

$$k > 2 \cdot 2^{N+1} - 2 \cdot 2^{-M} = k'.$$

Bild 2.7 Duale Zahlendarstellung im Rechner

Die kleinstmögliche Komplementärzahl ist damit

$$k_1 = k' + 2^{-M} = 2^{N+2} - 2^{-M}.$$

Negative Zahlen, die mit dieser Komplementärzahl gebildet werden, heißen *Einerkomplement*.

Die nächstmögliche Komplementärzahl ist:

$$k_2 = k_1 + 2^{-M} = 2^{N+2}.$$

Zahlen, die mit  $k_2$  gebildet werden, nennt man *Zweierkomplement*. In unserem Beispiel nach Bild 2.5 sind  $M = 0$  und  $N = 6$  und damit  $k_2 = 2^8$ .

### 2.2.1.5. Zahlensysteme mit der Basis 8 (Oktalsystem) und 16 (Hexadezimalsystem)

Sehr häufig werden zur übersichtlichen Darstellung von Dualzahlen dem Dualsystem verwandte Zahlensysteme verwendet. Hierzu gehören das Oktalsystem und das Hexadezimalsystem.

#### Oktaldarstellung

Beim Oktalsystem beträgt die Basis  $B = 8$ . Da  $8 = 2^3$  ist, bilden immer 3 Dualziffern eine Oktalziffer. Im Oktalsystem werden 7 Ziffern (0 bis 7) benötigt.

#### Beispiel

Die Dezimalzahl 201 lautet als Dualzahl 11001001 und als Oktalzahl 311 (11/001/001).

#### Hexadezimaldarstellung

Das Hexadezimalsystem hat die Basis  $B = 16$ . Da  $16 = 2^4$  ist, bilden 4 Dualziffern eine Hexadezimalziffer. Im Hexadezimalsystem werden 16 Ziffern benötigt. Für die Ziffern (10), (11), (12), (13), (14), (15) setzt man gewöhnlich die Zeichen A, B, C, D, E, F ein.

#### Beispiel

Die Dezimalzahl 201 lautet als Hexadezimalzahl C9 (1100/1001).

### 2.2.1.6. Zifferncode

Um Zahlen binär auszudrücken, gibt es außer der reinen Dualdarstellung noch gemischte Formen, sogenannte Codierungen, in

denen die Ziffern einer Dezimalzahl getrennt durch Binärziffern dargestellt werden.

Der einfachste Code ist der *BCD-Code* (Binär-Code), in dem jede Ziffer durch die entsprechende Dualzahl dargestellt wird. Für eine Ziffer werden dabei 4 Dualstellen benötigt.

### *Beispiel*

|      |              |      |      |      |      |

|------|--------------|------|------|------|------|

| 3791 | $\triangleq$ | 0011 | 0111 | 1001 | 0001 |

|      |              | 3    | 7    | 9    | 1    |

Die für eine Dezimalziffer notwendigen Dualstellen nennt man eine *Tetrad*. Mit diesen 4 Stellen lassen sich außer den Ziffern 0 bis 9 noch die Zahlen 10 bis 15 realisieren. Tritt innerhalb der Tetrad eine Kombination von Binärstellen auf, die einer der Zahlen 10 bis 15 entspricht (z. B. 1101  $\triangleq$  13), so nennt man diese Kombination eine *Pseudotetrad*. **Pseudotetraden sind Kombinationen von Binärziffern, deren Wert keiner der Ziffern 0 bis 9 zugeordnet ist.**

Außer dem BCD-Code gibt es noch weitere Codierungsvorschriften für Ziffern, in denen andere Kombinationen von Binärziffern den Dualziffern 0 bis 9 zugeordnet sind.

### **3-Exzeß-Code**

Codewert = Dualwert + 3.

Die 3-Exzeß-Code-Verschlüsselung ergibt für die Dezimalziffern 0 bis 9 folgende Zuordnung:

|   |      |

|---|------|

| 0 | 0011 |

| 1 | 0100 |

| 2 | 0101 |

| 3 | 0110 |

| 4 | 0111 |

| 5 | 1000 |

| 6 | 1001 |

| 7 | 1010 |

| 8 | 1011 |

| 9 | 1100 |

### **Aiken-Code**

Codewert = Dualwert, falls Zahlenwert < 5,

Codewert = Dualwert + 6, falls Zahlenwert  $\geq 5$ .

Der Aiken-Code ergibt für die Dezimalziffern 0 bis 9 folgende Zuordnung:

|   |      |

|---|------|

| 0 | 0000 |

| 1 | 0001 |

| 2 | 0010 |

| 3 | 0011 |

| 4 | 0100 |

| 5 | 1011 |

| 6 | 1100 |

| 7 | 1101 |

| 8 | 1110 |

| 9 | 1111 |

Außer der Darstellung von Dezimalziffern durch 4 Dualstellen gibt es noch solche mit mehr als 4 Dualstellen.

Beispiele solcher Codierungen sind der *Walking-Code* und der *Positionscode*.

### **Walking-Code (2-aus-5-Code)**

|     |           |

|-----|-----------|

| 0 = | 0 0 0 1 1 |

| 1 = | 0 0 1 0 1 |

| 2 = | 0 0 1 1 0 |

| 3 = | 0 1 0 1 0 |

| 4 = | 0 1 1 0 0 |

| 5 = | 1 0 1 0 0 |

| 6 = | 1 1 0 0 0 |

| 7 = | 0 1 0 0 1 |

| 8 = | 1 0 0 0 1 |

| 9 = | 1 0 0 1 0 |

### **Positionscode (1-aus-10-Code)**

|     |                       |

|-----|-----------------------|

| 0 = | 0 0 0 0 0 0 0 0 0 0 1 |

| 1 = | 0 0 0 0 0 0 0 0 0 1 0 |

| 2 = | 0 0 0 0 0 0 0 0 1 0 0 |

| 3 = | 0 0 0 0 0 0 0 1 0 0 0 |

| 4 = | 0 0 0 0 0 0 1 0 0 0 0 |

| 5 = | 0 0 0 0 0 1 0 0 0 0 0 |

| 6 = | 0 0 0 0 1 0 0 0 0 0 0 |

| 7 = | 0 0 0 1 0 0 0 0 0 0 0 |

| 8 = | 0 0 1 0 0 0 0 0 0 0 0 |

| 9 = | 0 1 0 0 0 0 0 0 0 0 0 |

### **2.2.1.7. Zahlenbereich im Rechner**

Bei der Darstellung von Zahlen im Rechner muß man die Tatsache berücksichtigen, daß ein Rechner nur eine bestimmte Stellenzahl hat. Stehen z. B. nur 7 Stellen für positive Dualzahlen zur Verfügung, wie es bei vielen Mikroprozessoren der Fall ist, so kann man damit nur ganze Zahlen zwischen 0 und 127 darstellen. Sollen auch gebrochene Zahlen dargestellt werden, so kann man das Komma vor eine dieser Stellen setzen. Dabei wird der Zahlenbereich nicht erweitert, sondern nur verschoben. Steht bei 7 Stellen das Komma nach der 4. Stelle, so kann man nur Zahlen zwischen 0 und 15,875 in Schritten zu 0,125 darstellen.

Damit der Zahlenbereich an die praktischen Erfordernisse angepaßt wird, gibt es noch verschiedene Darstellungsformen innerhalb eines Zahlensystems, die wichtigsten sind die *Festkomma*- und die *Gleitkommazahlen*.

#### **Festkommazahlen**

Dabei handelt es sich um Zahlen, bei denen eine feste Anzahl von Ziffern vor und nach dem Komma vereinbart wird. Die Stellung des Kommas und die Gesamtzahl der Ziffern hängt vom Rechner-typ ab. Es gibt auch Rechner, bei denen das Komma durch Tasten oder selbständig gesetzt wird.

#### **Beispiel**

In jedem Taschenrechner sind Dezimalzahlen der Form 3 7 2 8 3 · 6 1 3 üblich. In diesem Fall rechnet der Taschenrechner mit 8 Dezi-malstellen in Festkommadarstellung.

Im Dualsystem besteht das gleiche Problem. In einem Rechner läßt sich wegen der technischen Gegebenheiten nur eine feste Anzahl von Dualstellen speichern. Dabei kann das Komma rechts von der niedrigsten Stelle (dann handelt es sich um ganze Zahlen) oder links vor der höchsten Stelle stehen (dann handelt es sich um echt gebrochene Zahlen), oder das Komma trennt einen ganzen und ei-nen gebrochenen Teil.

Bei der Addition und Subtraktion von Festkommazahlen müssen die Zahlen so verschoben werden, daß die Kommas untereinander stehen. Bei Multiplikation und Division muß man die Stelle des Kommas besonders bestimmen.

#### **Gleitkommazahlen**

Jede Zahl  $Z$  läßt sich in folgender Form darstellen:

$$Z = m \cdot B^E$$

(z. B.  $0,19 \cdot 10^{-18}$ ;  $m = 0,19$ ;  $E = -18$ ;  $B = 10$ ).

Dabei nennt man  $m$  die *Mantisse*,  $E$  den *Exponenten*, und  $B$  ist die *Basis* des Zahlensystems.

Bei der dualen Darstellung von Gleitkommazahlen gilt für  $m$  bei den meisten Rechnern folgende Vorschrift:

1.  $-1 < m < +1$ .

2. Die 1. Stelle nach dem Komma soll nicht 0 sein.

Zahlen, die diesen Bedingungen genügen, nennt man *normalisierte Zahlen*. Durch diese Vorschrift werden die Mantisse  $m$  und der Exponent  $E$  eindeutig bestimmt. Es gibt aber auch Vorschriften für die Bildung der Mantisse  $m$ , die von der genannten Vorschrift abweichen.

### *Beispiel 1*

Man schreibe die Zahl 25,211 als Dezimalzahl in Gleitkommadarstellung.

Lösung:  $25,211 = 0,25211 \cdot 10^2$ .

Die Mantisse lautet also  $m = 0,25211$  und der Exponent  $E = 2$ .

### *Beispiel 2*

Man schreibe die Zahl 4,25 als Gleitkommazahl in dualityer Darstellung.

Lösung:  $4,25 = 1 \cdot 2^2 + 0 \cdot 2^1 + 0 \cdot 2^{-1} + 1 \cdot 2^{-2}$ .

Das ergibt die Dualzahl 100,01.

Als Gleitkommazahl entsprechend obiger Vorschrift wird daraus  $0,10001 \cdot 2^3 = 0,10001 \cdot 2^{11}$ .

Die Mantisse lautet also  $m = 0,10001$  und der Exponent  $E = 11$ .

## **2.2.2. Darstellung von Text (Zeichencode)**

Damit der Rechner beliebige Textinformationen speichern kann, müssen alphanumerische Zeichen auch durch Bit-Folgen (Folgen aus den Ziffern 0 und 1) dargestellt werden. Dabei ergibt sich die Frage, wieviel Dualstellen insgesamt zur Codierung aller vorkommenden Zeichen notwendig sind. Aus der Mathematik ist bekannt, daß mit  $n$  Dualstellen  $2^n$  unterschiedliche Bit-Folgen, bestehend

aus den Ziffern 0 und 1, dargestellt werden können. Nimmt man an, daß die Anzahl der verwendeten Zeichen (Buchstaben, Ziffern und Syntaxzeichen) kleiner als 128 ist, so benötigt man dazu 7 Dualstellen, da  $2^7 = 128$  ist. Meistens kommt zu diesen 7 Bit eine Kontrollbit hinzu. Die Bit-Folge von 8 Dualstellen nennt man 1 *Byte*. Innerhalb dieser 8 Stellen wird jedem Zeichen eine feste Folge aus den Ziffern 0 und 1 zugeordnet. Diese Folge ist der Code des betreffenden Zeichens.

Es gibt mehrere internationale Festlegungen für solche Zuordnungen. Die in der DDR am häufigsten verwendeten Zeichencode sind:

- SIF-1000-Code (Standard-Interface-Code für Datenverarbeitungsperipherie);

- ASCII-Code (American Standard Code for Information Interchange – amerikanischer Code für Informationsaustausch);

- R-300-Code;

- ISO-7-Bit-Code.

In Mikrorechnern wird vorwiegend der ASCII-Code und der SIF-1000-Code angewendet.

### 2.2.3. Rechnen mit Dualzahlen

#### Addition

Während bei Dezimalzahlen ein Übertrag entsteht, wenn die Summe zweier Ziffern größer als 9 ist, tritt im Dualsystem der Übertrag bereits auf, wenn die Summe größer als 2 ist. Im Dualsystem gelten folgende Grundregeln:

$$0 + 0 = 0 \text{ mit Übertrag } 0;$$

$$0 + 1 = 1 \text{ mit Übertrag } 0;$$

$$1 + 0 = 1 \text{ mit Übertrag } 0;$$

$$1 + 1 = 0 \text{ mit Übertrag } 1.$$

#### Beispiel

Bilden der Summe 13 + 7.

|                                                 |                                                                                 |

|-------------------------------------------------|---------------------------------------------------------------------------------|

| 1 Übertrag                                      | 1111 Übertrag                                                                   |

| Dezimal: 13                                     | Dual: $13 \triangleq 1101$                                                      |

| $\begin{array}{r} + 7 \\ \hline 20 \end{array}$ | $\begin{array}{r} + 7 \triangleq 111 \\ \hline 20 \triangleq 10100 \end{array}$ |

## Subtraktion

Gelingt die Subtraktion in einer Stelle nicht direkt, so muß der Minuend durch „Borgen“ aus der nächsthöheren Stelle erhöht werden. Im Dualsystem wird das „Borgen“ aus der nächsthöheren Stelle dadurch realisiert, daß von der höherwertigen Stelle, wie auch im Dezimalsystem, eine 1 abgezogen und dafür die betreffende Stelle um 10 erhöht wird

### Beispiel

Bilden der Differenz 91 – 53.

|                                                  |                                                                                                                                                                  |                                                                                                                     |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Dezimal: 91                                      | $\overset{\sim}{\text{1 geborgt}}$                                                                                                                               | Dual: 91 $\triangleq \overset{\sim}{1} \overset{\sim}{0} \overset{\sim}{1} \overset{\sim}{1} 0 \overset{\sim}{1} 1$ |

| $\begin{array}{r} - 53 \\ \hline 38 \end{array}$ | $\begin{array}{r} - 53 \triangleq 1 \overset{\sim}{1} 0 \overset{\sim}{1} 0 \overset{\sim}{1} 1 \\ \hline 38 \triangleq 1 0 0 1 \overset{\sim}{1} 0 \end{array}$ | $\overset{\sim}{1} \overset{\sim}{0} \overset{\sim}{0} \overset{\sim}{1} 1 0$ geborgt                               |

Werden negative Dualzahlen im Komplement dargestellt, dann realisiert man die Subtraktion durch die Addition im Zweierkomplement. Die Zahl –53 sieht in Zweierkomplementdarstellung folgendermaßen aus:

$$-53 \triangleq 1 1 0 0 1 0 1 1 ,$$

wobei das vorderste Bit die Vorzeichenstelle ist.

Das Beispiel 91 – 53 sieht, wenn statt 91 – 53 91 + (–53) gerechnet wird, so aus:

$$\begin{array}{r} 91 \triangleq 0 1 0 1 1 0 1 1 \\ -53 \triangleq 1 1 0 0 1 0 1 1 \\ \hline 0 0 1 0 0 1 1 0 \end{array}$$

Der Übertrag in die Stelle vor dem Vorzeichen wird dabei nicht mehr berücksichtigt, da er über die vorgegebene Stellenzahl hinausgeht. Zur Begründung der angewandten Methode setzt man für eine negative Zahl  $y$  in der Komplementdarstellung das Zeichen  $y'$ . Dann ist  $y' = y + k_2$ , mit  $k_2 = 2^8$ , wenn es sich um das Zweierkomplement handelt.

Die Zahl  $k_2 = 2^8$  lässt sich mit den vorgegebenen Stellen nicht darstellen, da der höchste Stellenwert  $2^7$  ist.

Für  $x - y$  gilt:

$$x - y = x + (-y) = x + y' = x - y + k_2 .$$

Ist  $x - y$  negativ, so steht das Ergebnis mit  $x - y + k_2$  richtig im Register. Ist  $x - y$  positiv, so ergibt sich ebenfalls ein richtiges Ergebnis, da die Stelle für  $k_2$  nicht vorhanden ist.

Sind  $x$  und  $y$  negativ, dann gilt:

$$-x - y = x' + y' = -x - y + 2k_2 = -x - y + k_2 + k_2.$$

Der Wert  $-x - y + k_2$  ist die Komplementdarstellung von  $-x - y$ . Das zweite  $k_2$  wird nicht im Register dargestellt, da die dafür notwendige Stelle nicht vorhanden ist.

## Multiplikationen

Zur Multiplikation müssen die beiden Operanden positiv sein. Die Multiplikation von positiven Zahlen gleicht der im Dezimalsystem, wobei folgende Grundregeln gelten:

$$0 \cdot 0 = 0;$$

$$0 \cdot 1 = 0;$$

$$1 \cdot 0 = 0;$$

$$1 \cdot 1 = 1.$$

Die Multiplikation ist eine fortgesetzte Addition, wobei die einzelnen Summanden entsprechend ihrem Stellenwert verschoben sind.

### Beispiel

Bilden des Produkts  $12 * 5$ .

$$\begin{array}{r} 1100 * 101 \\ 0000 \end{array}$$

$$\begin{array}{r} 1100 \\ \hline 111100 \end{array}$$

$$60 \leqq 111100$$

Auch hier kann wie beim Rechnen mit Dezimalzahlen im angegebenen Beispiel die Nullzeile weggelassen werden.

## Division

Die Division ist im wesentlichen eine fortgesetzte Subtraktion. In den Quotienten wird dann eine Ziffer 1 eingetragen, wenn der Subtrahend kleiner als der Minuend ist. Da die Subtraktion auch als Addition im Komplement realisiert werden kann, ergeben sich unterschiedliche Verfahren für die Division, die jedoch im Prinzip auf der gleichen Grundlage beruhen.

### Beispiel 1

Bilden der Division  $108 : 12$  nach dem normalen Handrechenverfahren.

$$\begin{array}{r} 1101100 : 1100 = 1001 \\ - 1100 \quad \text{geht zu subtrahieren} \\ \hline 0001100 \quad (\text{Subtrahend ist kleiner als} \\ \quad \quad \quad \text{Minuend}), \text{ Ergebnis ist } 1; \\ \quad \quad \quad \text{Rest} \end{array}$$

### Divisor 1 Stelle

|             |                                                        |                                                        |

|-------------|--------------------------------------------------------|--------------------------------------------------------|

| nach rechts | $\begin{array}{r} -1100 \\ \hline 0001100 \end{array}$ | geht nicht zu subtrahieren,<br>Ergebnis ist 0;<br>Rest |

| nach rechts | $\begin{array}{r} -1100 \\ \hline 0001100 \end{array}$ | geht nicht zu subtrahieren,<br>Ergebnis ist 0;<br>Rest |

| nach rechts | $\begin{array}{r} -1100 \\ \hline 0000000 \end{array}$ | geht zu subtrahieren,<br>Ergebnis ist 1;<br>Rest       |

Da der Rest 0 ist, lautet das Ergebnis 1 0 0 1 .

### Beispiel 2

Bilden der Division 108 : 12 mit Rückstellung des Restes unter Verwendung der Komplementdarstellung.

$$1101100 : 1100 = 1001$$

|             |                          |                                                                                                                    |

|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| Stellenzahl | $876543210$              |                                                                                                                    |

|             | $01101100$               | Divident                                                                                                           |

|             | $+ \underline{10100000}$ | Zweierkomplement des Divisors                                                                                      |

|             | $00001100$               | Ergebnis ist positiv – ergibt eine 1 im Quotienten                                                                 |

|             | $+ 11010000$             | Divisor um eine Stelle nach rechts verschoben<br>(Zweierkomplement)                                                |

|             | $11011100$               | Ergebnis ist negativ – ergibt eine 0 im Quotienten                                                                 |

|             | $+ \underline{1100}$     | Da das vorangegangene Ergebnis negativ ist, muß der Divisor wieder dazugezählt werden<br>(Rückstellung des Restes) |

|             | $00001100$               |                                                                                                                    |

|             | $+ \underline{11101000}$ | Divisor um eine Stelle nach rechts verschoben,                                                                     |

|             | $11110100$               | Ergebnis ist negativ – ergibt eine 0 im Quotienten                                                                 |

$$\begin{array}{r}

+ \quad 1 \ 1 \ 0 \ 0 \\

\hline

0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0 \\

+ \underline{1 \ 1 \ 1 \ 1 \ 0 \ 1 \ 0 \ 0} \\

\hline

0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0

\end{array}$$

Da das vorangegangene Ergebnis negativ ist, muß der Divisor wieder dazugezählt werden

(Rückstellung des Restes)

Divisor um 1 nach rechts verschoben

Ergebnis positiv – ergibt 1 im Quotienten

Der verbleibende Rest ist 0, die Division geht auf und ergibt den Quotienten 1001.

Geht man von der Tatsache aus, daß Multiplikation und Division durch fortgesetzte Additionen bzw. Subtraktionen realisiert werden, so läßt sich zeigen, daß im Dualsystem weniger Additionen und Subtraktionen notwendig sind als im Dezimalsystem.

### **Rechnen mit codierten Zahlen**

In diesem Abschnitt wird nur auf BCD-codierte Zahlen eingegangen, da der BCD-Code der am häufigsten verwendete Code ist. Für die Rechenoperationen im BCD-Code gibt es bei den Mikroprozessoren 8080 und U880 spezielle Befehle. Werden 2 Dezimalziffern im BCD-Code addiert, so können folgende Fälle auftreten:

1. Die Summe ist  $\leq 9$ .

2. Die Summe ist  $> 9$  aber  $\leq 15$ .

3. Die Summe ist  $> 15$ .

Im Fall 1 ist die Ergebnisziffer richtig.

#### *Beispiel*

Summe 4 + 5:  $4 \triangleq 0100$

$$\begin{array}{r}

5 \triangleq 0101 \\

\hline

9 \triangleq 1001

\end{array}$$

Im Fall 2 ist die Ergebnisziffer eine Pseudotetrad. Die richtige Ziffer erhält man durch Addition von 6.

#### *Beispiel*

Summe 7 + 6:  $7 \triangleq 0111$

$$\begin{array}{r}

6 \triangleq 0110 \\

\hline

1101 = \text{Pseudotetrad} \\

+ \quad 110 \quad (\text{Addition 6}) \\

\hline

13 \triangleq 10011

\end{array}$$

Im Fall 3 ergibt sich bereits der richtige Übertrag, aber die Ergebnisziffer muß noch um 6 erhöht werden.

### *Beispiel*

$$\begin{array}{rcl} \text{Summe } 8+9: & 8 \triangleq & 1000 \\ & 9 \triangleq & 1001 \end{array}$$

Übertrag in die

nächste Dezi-

malziffer —

$$+ \quad 110 \text{ (Addition 6)}$$

Für die Addition im BCD-Code lassen sich also folgende Regeln aufstellen:

Ergibt die Summe zweier Ziffern plus Übertrag von der vorherigen Stelle keine Pseudotetrad und keinen Übertrag in die nächste Dezimalstelle, so ist die Ergebnisziffer richtig.

Ergibt die Summe zweier Ziffern eine Pseudotetradie oder einen Übertrag in die nächste Stelle, dann muß die Ergebnisziffer um 6 erhöht werden.

## *Beispiel*

$$\text{Summe} \quad 2985 + 4936 = 7921.$$

|         |            |                          |                                |

|---------|------------|--------------------------|--------------------------------|

|         |            |                          | Übertrag in<br>nächste Tetrade |

| 0 0 1 0 | 1 0 0 1    | 1 0 0 0                  |                                |

| 0 1 0 0 | 1 0 0 1    | 0 0 1 1                  |                                |

| 0 1 1 1 | 0 0 1 1    | 1 1 0 0 $\triangleq$ PS* |                                |

|         | 1 1 0 (+6) |                          | 1 0 1 1 $\triangleq$ PS*       |

| 0 1 1 1 | 1 0 0 1    | 1 1 0 (+6)               | 1 1 0 (+6)                     |

|         |            | 0 0 1 0                  | 0 0 0 1 $\triangleq$ 7921      |

\* PS = Pseudotetradec

## Rechnen mit Gleitkommazahlen

## Addition und Subtraktion von Gleitkommazahlen

Die Addition bzw. Subtraktion der Mantissen zweier Zahlen ist nur dann möglich, wenn die Exponenten beider Zahlen gleich sind.

Für die Berechnung von

$$Z_1 + Z_2 = m_1 \cdot 10^{E1} + m_2 \cdot 10^{E2}$$

muß unter der Voraussetzung, daß  $E_1 < E_2$  ist,  $m_1$  um  $E_2 - E_1$

Stellen nach rechts verschoben werden. Die neue Mantisse sei mit  $m'_1$  bezeichnet, dann ist

$$Z_1 + Z_2 = m'_1 \cdot 10^{E2} + m_2 \cdot 10^{E2} = (m'_1 + m_2) \cdot 10^{E2}.$$

Die neue Mantisse ist also  $m'_1 + m_2$ , der neue Exponent  $E_2$ .

### *Beispiel*

$$Z_1 = 0,25 \cdot 10^2;$$

$$Z_2 = 0,35 \cdot 10^4.$$

$E_2 - E_1 = 2$ , d. h., die Mantisse von  $Z_1$  muß um 2 Stellen nach rechts verschoben werden. Es gilt also:

$$\begin{aligned} Z_1 + Z_2 &= 0,25 \cdot 10^2 + 0,35 \cdot 10^4 \\ &= 0,0025 \cdot 10^4 + 0,35 \cdot 10^4 = 0,3525 \cdot 10^4. \end{aligned}$$

Bei der Addition im Dualsystem verfährt man analog.

Bei der Subtraktion ist in entsprechender Weise vorzugehen.

### **Multiplikation von Gleitkommazahlen**

Die Multiplikation von Gleitkommazahlen läuft nach der Regel

$$Z_1 \cdot Z_2 = m_1 \cdot 10^{E1} \cdot m_2 \cdot 10^{E2} = m_1 \cdot m_2 \cdot 10^{E2 + E1}$$

ab. Die neue Mantisse ist also  $m_1 \cdot m_2$ , der neue Exponent  $E_1 + E_2$ .

Die neue Mantisse  $m_1 \cdot m_2$  darf ebenfalls keine 0 nach dem Komma aufweisen, d. h., gegebenenfalls ist die 0 nach dem Komma durch Verschiebung von  $m_1 \cdot m_2$  um ein Stelle nach links zu beseitigen, wobei der Exponent  $E_1 + E_2$  um 1 zu erniedrigen ist.

### *Beispiel 1 (Dezimalsystem)*

$$Z_1 = 0,2 \cdot 10^2;$$

$$Z_2 = 0,3 \cdot 10^3;$$

$$Z_1 \cdot Z_2 = 0,2 \cdot 0,3 \cdot 10^{2+3} = 0,06 \cdot 10^5 = 0,6 \cdot 10^4.$$

(Die „0“ nach dem Komma bei 0,06 wurde durch Verschiebung um eine Stelle nach rechts und Erniedrigung des Exponenten 5 um 1 beseitigt.)

Im Dualsystem wird in entsprechender Weise verfahren.

### *Beispiel 2 (Dualsystem)*

$$3 \cdot 4 = 12.$$

$$\begin{aligned} 3 \triangleq 11 &= 0,11 \cdot 2^2 = 0,11 \cdot 2^{10}; 4 \triangleq 100 = 0,1 \cdot 2^3 = 0,1 \cdot 2^{11}; \\ 0,11 \cdot 2^{10} \cdot 0,1 \cdot 2^{11} &= 0,11 \cdot 0,1 \cdot 2^{10+11} = 0,011 \cdot 2^{101}; \\ &= 0,11 \cdot 2^{(101-1)} = 0,11 \cdot 2^{100}. \end{aligned}$$

### **Division von Gleitkommazahlen**

Die Division von Gleitkommazahlen läuft nach der Regel

$$\frac{Z_1}{Z_2} = \frac{m_1 \cdot 10^{E1}}{m_2 \cdot 10^{E2}} = \frac{m_1}{m_2} \cdot 10^{E1 - E2}$$

ab. Die neue Mantisse ist also  $m_1 : m_2$ , der neue Exponent  $E_1 - E_2$ . Da die neue Mantisse der Vorschrift  $-1 < m < +1$  genügen muß, ist gegebenenfalls die Ergebnismantisse um eine Stelle nach rechts zu verschieben und der Exponent dabei um 1 zu erhöhen.

### *Beispiel 1 (Dezimalsystem)*

$$Z_1 = 0,25 \cdot 10^2;$$

$$Z_2 = 0,5 \cdot 10^1;$$

$$\frac{Z_1}{Z_2} = \frac{0,25 \cdot 10^2}{0,5 \cdot 10^1} = \frac{0,25}{0,5} \cdot 10^{2-1} = 0,5 \cdot 10^1.$$

### *Beispiel 2 (Dualsystem)*

$$6 : 2 = 3$$

$$Z_1 = 6 \triangleq 0,11 \cdot 2^{11};$$

$$Z_2 = 2 \triangleq 0,1 \cdot 2^{10};$$

$$\frac{Z_1}{Z_2} = \frac{0,11 \cdot 2^{11}}{0,1 \cdot 2^{10}} = \frac{0,11}{0,1} \cdot 2^{11-10} = 1,1 \cdot 2^1 = 0,11 \cdot 2^{1+1} = 0,11 \cdot 2^{10}.$$

## **2.3. Aufbau der Befehle**

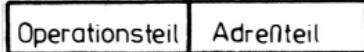

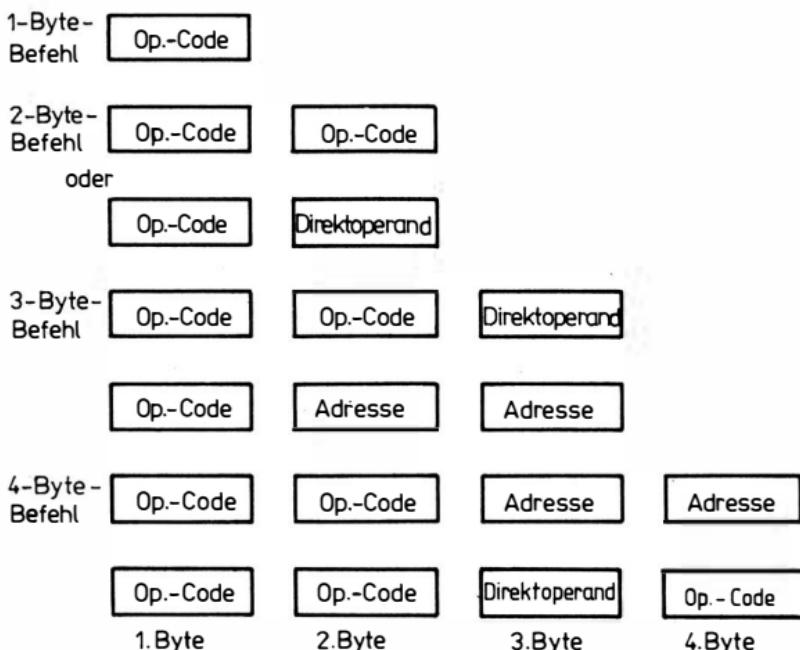

Genauso wie die Zahlen durch Bit-Folgen dargestellt werden, muß man auch die Anweisungen (Befehle) in Bit-Folgen umwandeln, um sie zu speichern. Da eine Anweisung (Befehl) eine Information sein soll, aus der hervorgeht, was der Rechner zu tun hat, besteht sie aus 2 Hauptteilen:

- Der 1. Teil sagt aus, was bzw. welche Operation der Rechner ausführen soll.

- Der 2. Teil sagt aus, woher die Daten kommen, die für die Durchführung dieser Operation gebraucht werden.

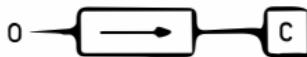

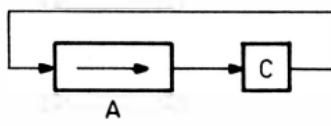

Der 1. Teil wird *Operationsteil*, der 2. Teil *Adressteil* genannt (Bild 2.8). Im Adressteil steht eine Adresse (Einadreßbefehl) oder mehrere Adressen (Mehradreßbefehl) für die benötigten Daten. Im Adressteil eines Einadreßbefehls steht entweder die fertige Adresse oder, wie es oft der Fall ist, eine Rechenvorschrift, aus der die endgültige Adresse ermittelt wird. Man spricht in diesem Fall

Bild 2.8 Befehlsaufbau

von *Adreßrechnung*. Durch die Adreßrechnung wird aus den im Adreßteil des Befehls stehenden Angaben die endgültige Speicheradresse ermittelt.

Bei der Adreßrechnung gibt es 2 Grundprinzipien, auf die bei nahezu allen Rechnern zurückgegriffen wird. Das erste Prinzip ist unter dem Namen *Index-Rechnung* bekannt. Bei der Index-Rechnung wird die endgültige Speicheradresse ermittelt, indem zu der im Befehl angegebenen Adresse der Inhalt eines speziellen Registers, *Index-Register* genannt, dazugezählt wird. Die endgültige Speicheradresse ist also gleich im Befehl angegebene Adresse plus Inhalt Index-Register (Indexierung):

**Endgültige Speicheradresse = im Befehl angegebene Adresse + <Index-Register>.**

Das zweite Prinzip ist unter dem Namen *indirekte Adressierung* bekannt. Bei der indirekten Adressierung steht die endgültige Speicheradresse in der Zelle, deren Adresse im Befehl steht; oder anders ausgedrückt, die endgültige Adresse ist der Inhalt der im Befehl angegebenen Speicherzelle. Es kommt auch vor, daß die endgültige Adresse nicht in der Speicherzelle, sondern in einem speziellen Register steht.

**Endgültige Speicheradresse = Inhalt der im Befehl angegebenen Speicherzelle.**

## 2.4. Befehlsschlüssel eines Rechners

Der Befehlsschlüssel ist eine Zusammenfassung aller Befehle, die ein Rechner ausführen kann. Jedem Befehl wird eine bestimmte Bit-Folge im Operationsteil zugeordnet. Diese Bit-Folge nennt man *Operationscode*. Bei Befehlen, die keinen Speicherzugriff benötigen (*nichtspeicherbezogene Befehle*), wird zur Codierung des Befehls der Adreßteil hinzugezogen. Die folgende Zusammenstellung enthält eine Übersicht über Befehlsarten, die ein Mikroprozessor ausführen kann.

### – Adreßoperationen

Adreßoperationen sind Operationen zur Ermittlung der endgül-

tigen Speicheradresse aus den Angaben im Adreßteil des Befehls (Indexierung, indirekte Adressierung).

#### – *Transportoperationen*

Transportoperationen dienen zur Übertragung von Daten vom Speicher in spezielle Register und umgekehrt oder von Speicherzellen in andere Speicherzellen. Man unterscheidet *Einzelworttransfer* und *Blocktransfer*. Einzelworttransfer ist die Übertragung eines Wortes oder Bytes, Blocktransfer ist die Übertragung eines Datenblocks von einem Speicherbereich in einen anderen Speicherbereich.

#### – *Rechen- und logische Operationen*

Diese Operationen dienen zur Verknüpfung von Zahlen bzw. Bit-Folgen. Bei den Rechenoperationen werden Zahlen durch Rechenvorschriften (Addition, Subtraktion, Multiplikation, Division), bei den logischen Operationen durch logische Operatoren (UND, ODER, NEGATION, EXKLUSIV-ODER usw.) verknüpft. Das Resultat steht meistens in einem speziellen Register, dem *Akkumulatorregister*.

Außerdem gibt es Befehle, durch die einzelne Bits einer Bit-Folge verändert werden, sowie Befehle zum Vergleich zweier Bit-Folgen.

#### *Sprungoperationen*

Sprungoperationen dienen zur Gestaltung der Programmstruktur. Durch einen Sprungbefehl ist es möglich, von einer Stelle im Programm an eine beliebige andere Stelle zu springen und dort die Abarbeitung fortzusetzen.

Natürliche Abarbeitungsfolge      Reihenfolge bei Sprungbefehl

Befehl 1

Befehl 1

Befehl 2

Befehl 2 (Sprung nach Befehl 5)

Befehl 3

.

Befehl 4

.

Befehl 5

→ Befehl 5

Befehl 6

Befehl 6

#### *Unterprogrammbefehle*

Ein Unterprogramm ist ein Programm, das eine spezielle Funktion ausführt, die während der Abarbeitung eines größeren Programms mehrmals notwendig ist (z. B. Berechnung des Logarithmus einer Zahl). Man spricht deshalb vom *Hauptprogramm*, das die gesamte Aufgabe realisiert, und vom *Unterprogramm* zur Lösung einer speziellen Funktion.

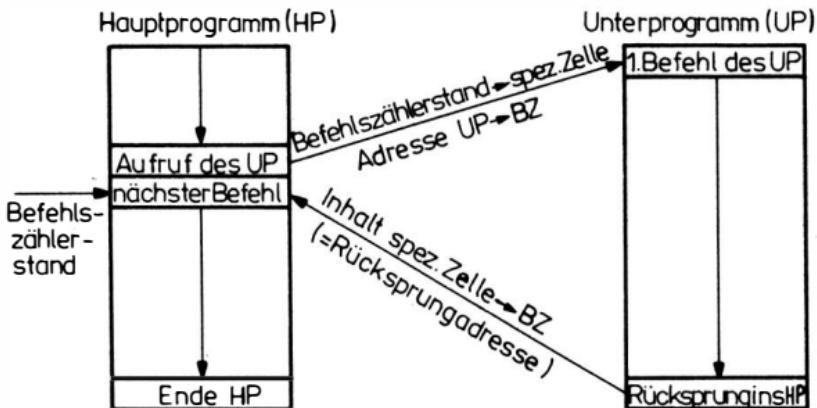

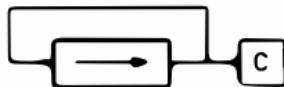

Bild 2.9 Arbeitsweise eines Unterprogramms

Das Unterprogramm steht nur einmal im Speicher und muß so arbeiten, daß man es von verschiedenen Stellen des Hauptprogramms aus aufrufen kann. Nach dem Durchlaufen des Unterprogramms muß an die Stelle im Hauptprogramm zurückgesprungen werden, von der aus ins Unterprogramm gesprungen wurde. Der Sprungbefehl ins Unterprogramm besteht aus 2 Funktionen. Erstens wird ein einfacher Sprung zur Startadresse des Unterprogramms ausgeführt, zweitens muß die Rücksprungstelle ins Hauptprogramm gemerkt werden. Die Rücksprungadresse (Inhalt Befehlszähler + 1) wird in einer speziellen Speicherzelle gemerkt.

Der Rücksprung aus dem Unterprogramm ist ein Sprungbefehl, dessen Adresse aus der Speicherzelle genommen wird, in der die Rücksprungadresse steht (Bild 2.9).

#### *Steueroperationen*

Diese Operationen sind spezielle Befehle, die den Zustand des Rechners festlegen. Dazu gehört z. B. der HALT-Befehl.

#### *Ein- und Ausgabeoperation*

Sie dienen zur Ansteuerung entsprechender Kanäle, an die Geräte zur Ein- bzw. Ausgabe von Daten angeschlossen sind.

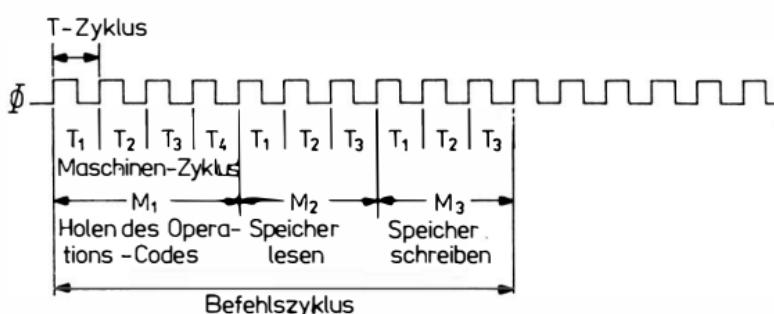

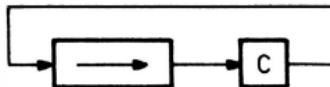

## 2.5. Befehlsabarbeitung

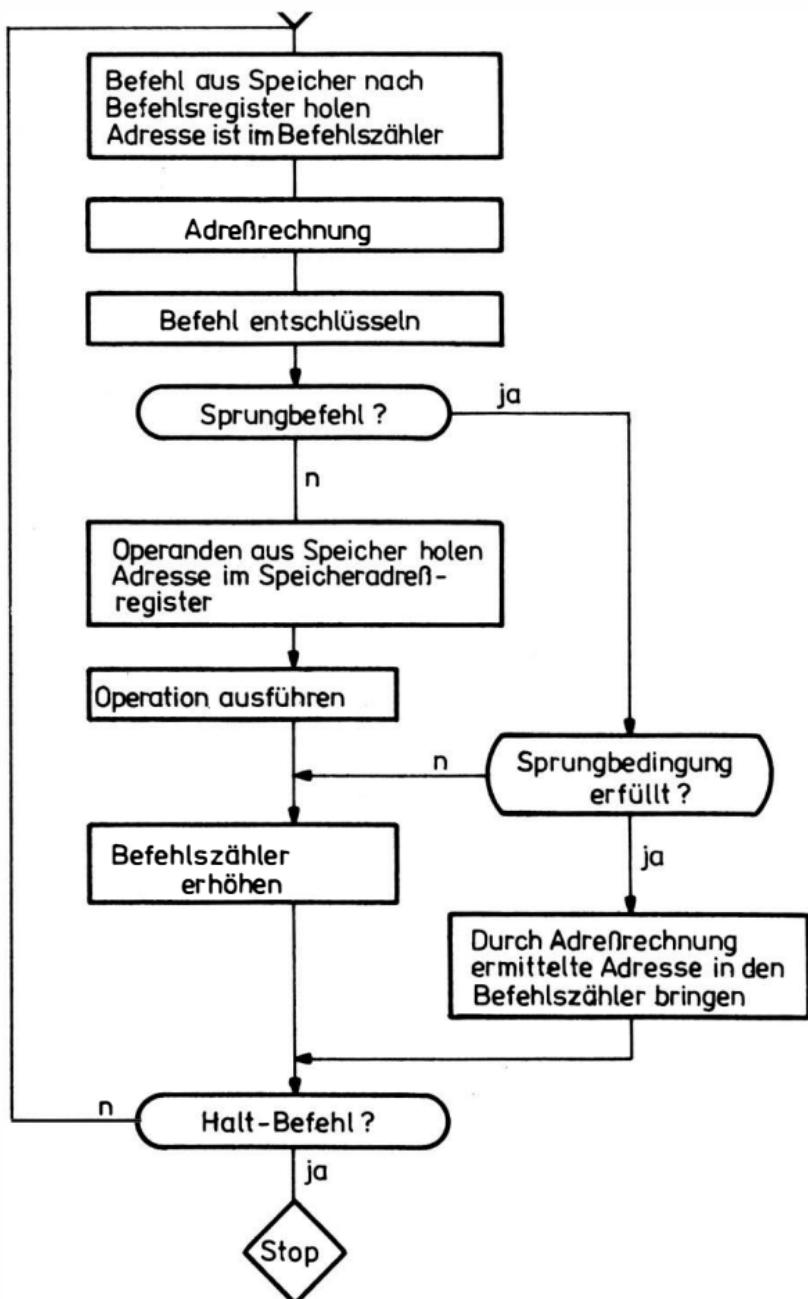

Zur Abarbeitung eines Programms werden die Befehle der Reihe nach aus dem Speicher in die CPU geholt. Die Adresse der Speicherzelle, aus der der Befehl kommt, steht im Befehlszähler (BZ). Die Ausführung eines Befehls geht in einzelnen Abschnitten, den

Bild 2.10 Befehlsabarbeitung

*Maschinenzyklen*, vor sich. Bild 2.10 zeigt, welche Funktionen bei der Ausführung eines Befehls abgearbeitet werden.

## 2.6. Ein- und Ausgabesteuerung (E/A-Steuerung)

### 2.6.1. Prinzip der E/A-Steuerung

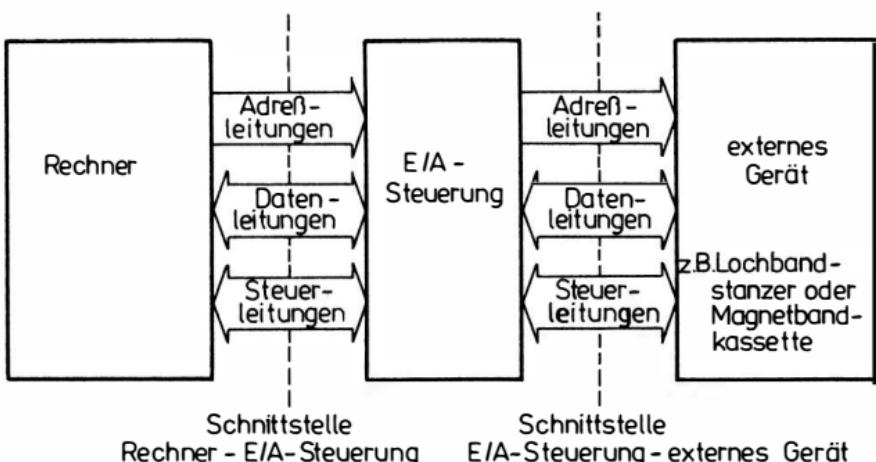

Die Ein-/Ausgabe-Steuerung stellt die Verbindung zwischen dem Rechner und den peripheren Geräten her (Bild 2.11).

Die Schnittstellen zwischen Rechner und E/A-Steuerung und zwischen E/A-Steuerung und externem Gerät bestehen aus Daten-, Adreß- und Steuerleitungen. Man spricht vom *Datenbus*, *Adreßbus* und *Steuerbus*. Ist an die E/A-Steuerung nur ein externes Gerät angeschlossen, dann kann der dazugehörige Adreßbus entfallen. Entsprechen die Leitungen einer Schnittstelle einer Normung, so spricht man von einer *Standard-Interface*.

#### Datenbus

Über den Datenbus werden Dateninformationen übertragen. Er besteht meistens aus 8 (1 Byte) oder 16 Leitungen.

#### Adreßbus

Der Adreßbus enthält die Adresse der E/A-Steuerung bzw. die Adresse des externen Geräts. Das Gerät entschlüsselt die Adresse und bildet ein Adreßsignal, wenn es durch die richtige Adresse angesprochen wird.

Bild 2.11 Ein-/Ausgabe-Steuerung

## *Steuerbus*

Der Steuerbus enthält Signale, die den Zeitpunkt der Datenübertragung festlegen. Es sind Melde- und Steuersignale. Meldesignale sind Ausgangssignale eines Geräteteils. Wichtige Meldesignale sind:

- Geräteteil für Daten empfangsbereit;

- Geräteteil hat Daten übernommen;

- Geräteteil hat Daten zur Ausgabe bereitgestellt;

- Fehler im Geräteteil.

Die Meldesignale des sendenden Geräteteils sind gleichzeitig Steuersignale für den empfangenden Geräteteil.

Der Datenaustausch geschieht im allgemeinen nach dem sogenannten *Hand-shake-Prinzip*. (Die anfordernde Stelle gibt ein Anforderungssignal (Request) und wartet, bis die Gegenstelle ein Quittungssignal zurückgibt.)

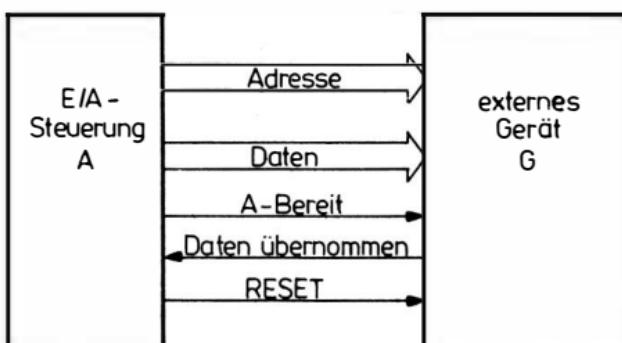

## *Beispiel*

Die E/A-Steuerung A gibt Daten an das Gerät G (Bild 2.12):

- Die E/A-Steuerung sendet die Adresse des Gerätes G und stellt die Daten auf dem Datenbus bereit.

- Die E/A-Steuerung sendet als Zeichen bereitstehender Daten das Signal „A-Bereit“.

- Das Gerät G entschlüsselt die Adresse und übernimmt, wenn es bereit ist, die Daten.

- Hat G die Daten übernommen, so sendet es das Signal „Daten übernommen“.

- Jetzt kann die E/A-Steuerung die Daten und die Adresse wieder abschalten.

Bild 2.12 Aufbau einer Interface-Schnittstelle

Die Signale „A-Bereit“ und „Daten übernommen“ sind Signale des Steuerbusses. Ein wichtiges Steuersignal ist das *Löschsignal* (RESET), mit dem vom Rechner aus alle angeschlossenen Geräte in die Ausgangsstellung gesetzt werden.

## 2.6.2. Programmierte Ein- und Ausgabe

Wird ein Rechnerwort vom Rechner über die E/A-Steuerung zum externen Gerät mit Hilfe eines Ein- oder Ausgabebefehls ein- oder ausgegeben, so spricht man von *programmierter Ein- bzw. Ausgabe*. Dabei wird meistens vom Datenbus ein Byte in ein Register der CPU eingegeben oder der Inhalt eines Registers auf den Datenbus bereitgestellt. Der Ein- bzw. Ausgabebefehl enthält die Richtung (Ein- oder Ausgabe) und die Geräteadresse. Für die programmierte Ein- und Ausgabe gibt es 4 Befehlsgruppen.

|                                                     |                                                                                                                                                    |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| E/A-Befehle Gruppe 1:<br><i>(E/A-Steuerbefehle)</i> | Durch den Befehl werden Funktionssignale zum externen Gerät gesandt, die dort eine bestimmte Funktion auslösen (z. B. Magnetbandkassette starten). |

| E/A-Befehle Gruppe 2:<br><i>(E/A-Testbefehle)</i>   | Durch den Befehl wird der Zustand des externen Geräts abgefragt und in Abhängigkeit vom Zustand ein bedingter Sprung ausgeführt.                   |

| E/A-Befehle Gruppe 3:<br><i>(Eingabebefehle)</i>    | Durch den Befehl wird die Eingabe eines Datenwertes vom Datenbus in ein spezielles Register der CPU realisiert.                                    |

| E/A-Befehle Gruppe 4:<br><i>(Ausgabebefehle)</i>    | Durch den Befehl wird der Inhalt eines speziellen Registers der CPU auf dem Datenbus bereitgestellt.                                               |

## 2.6.3. Autonome Ein- und Ausgabe

Die *autonome Ein- und Ausgabe* ist auch unter den Begriffen DSK (Direkter Speicherkanal) oder DMA (Direct Memory Access)

bekannt. Dabei geschieht die Ein- bzw. Ausgabe in Datenblöcken zwischen Speicher und externem Gerät mit Hilfe der E/A-Steuerung (*DMA-Steuerung* genannt).

Die DMA-Steuerung enthält folgende Register:

- Adreßregister zum Adressieren des Speichers;

- Datenregister (Datenpuffer) zur Zwischenspeicherung eines Wortes;

- Geräteadreßregister;

- Blocklängenregister.

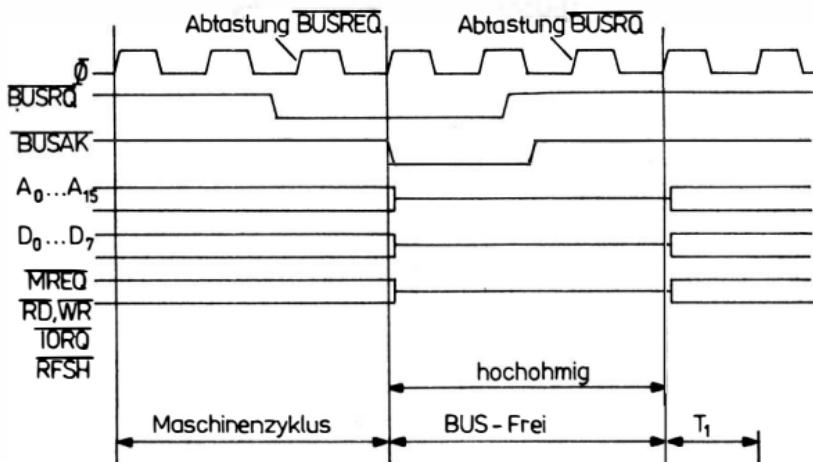

Vor dem Auslösen des autonomen Datentransfer werden über die programmierte Ausgabe Adreßregister, Geräteregister und Blocklängenregister mit den entsprechenden Werten gefüllt. Nach dem Start des autonomen Datentransfer geht der weitere Datenaustausch zwischen Speicher und externem Gerät mit Hilfe der DMA-Steuerung vor sich. Zwischen DMA-Steuerung und externem Gerät vollzieht sich der Datenaustausch wie beim programmierten Kanal im Hand-shake-Verfahren. Ist die DMA-Steuerung zum Datenaustausch mit dem Speicher bereit (Datenpuffer voll bei Eingabe, Datenpuffer leer bei Ausgabe), so erfolgt ein Speicherzugriff. Dazu läuft ein Speicherzyklus ab (Speicherzyklus: Adresse an Adressschlüsselung, Speicheranforderungssignal anlegen, Speicher auf Lesen oder Schreiben schalten, Daten auslesen oder einschreiben). Dieser Speicherzyklus wird bei Rechnern, in denen parallel zur autonomen Ein- und Ausgabe die Arbeit mit der CPU (*Central Processor Unit* = Rechenwerk und Steuerwerk) möglich ist, eingeschoben. Nach der Ein- bzw. Ausgabe des Datenblocks gibt die DMA-Steuerung ein „Endsignal“ ab.

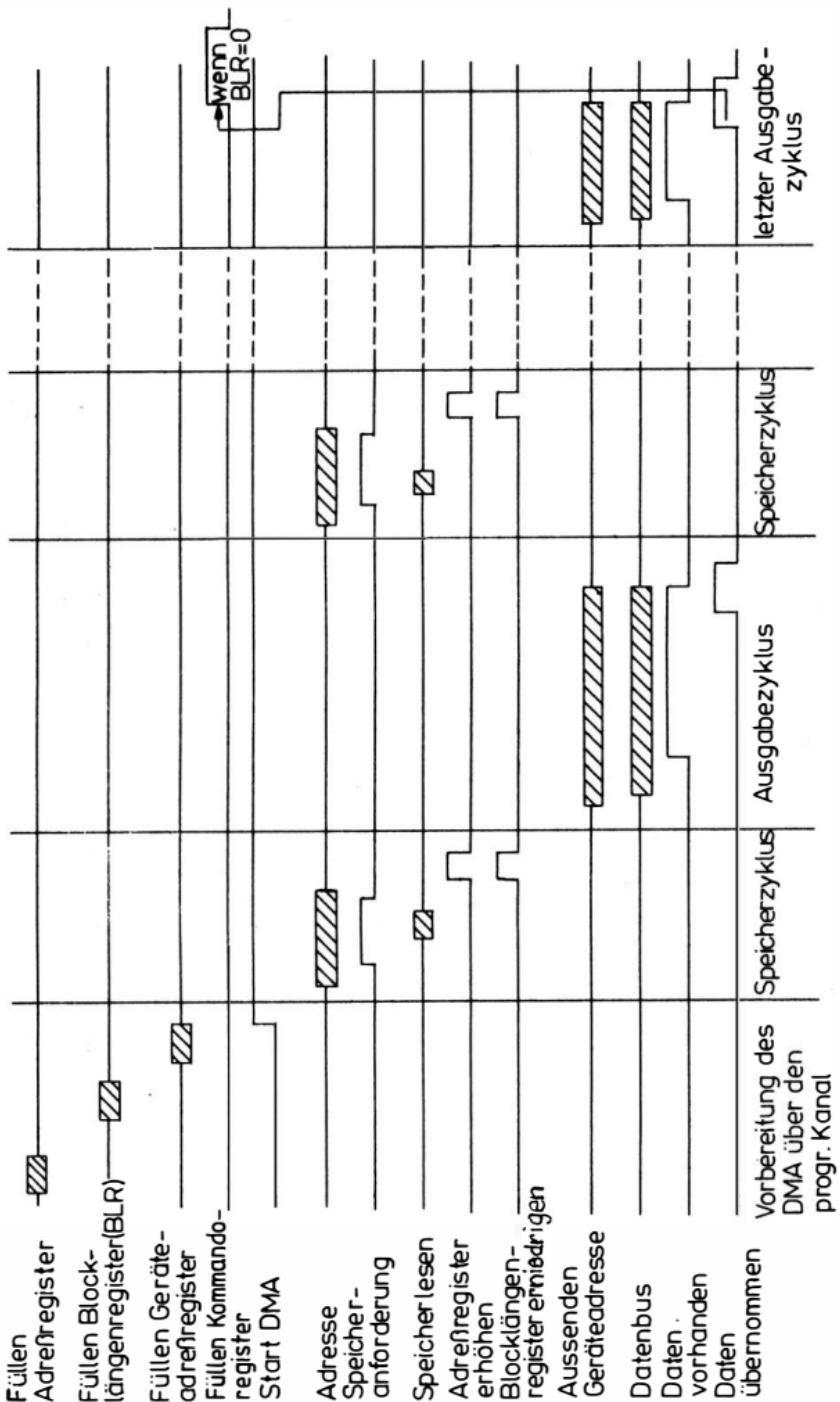

### *Beispiel*

Ausgabe eines Datenblocks vom Speicher. Dabei werden folgende Teilschritte ausgeführt:

- Einstellen des Grundzustands durch E/A-Befehle über den programmierten Kanal;

- a) Füllen des Adreßregisters mit der Anfangsadresse des Datenblocks,

- b) Füllen des Blocklängenregisters mit der Anzahl der Worte,

- c) Füllen des Geräteadreßregisters mit der Adresse des Ausgabegeräts (z. B. Drucker),

- d) Starten zur autonomen Datenausgabe.

Bild 2.13 Taktdiagramm einer Ausgabe über den DMA-Kanal

- Die DMA-Steuerung fordert einen Speicherzyklus;

- a) Adresse an Adreßentschlüsselung,

- b) Speicheranforderungssignal,

- c) Speicher lesen, Wort nach Datenpuffer,

- d) Inhalt des Adreßregisters um 1 erhöhen,

- e) Inhalt des Blocklängenregisters um 1 erniedrigen.

- Zwischen DMA-Steuerung und Ausgabegerät findet ein Handshake-Zyklus statt;

- a) die DMA-Steuerung sendet die Adresse des Ausgabegeräts und stellt die Daten auf dem Datenbus bereit,

- b) die DMA-Steuerung sendet das Signal „Daten vorhanden“,

- c) das Ausgabegerät übernimmt das Datenwort,

- d) das Ausgabegerät sendet „Daten übernommen“,

- e) die DMA-Steuerung schaltet das Signal „Daten vorhanden“ ab.

Speicherzyklus und Hand-shake-Zyklus zum Ausgabegerät werden so lange wiederholt, bis das Blocklängenregister Null ist. Jetzt sendet die DMA-Steuerung das „Endesignal“. Bild 2.13 zeigt das Taktdiagramm einer Ausgabe über den DMA-Kanal.

## 2.7. Programmunterbrechung (INTERRUPT)

Durch eine Programmunterbrechung besteht die Möglichkeit, den Programmablauf durch Signale von außen zu steuern. Ein in den Rechner gegebenes Programmunterbrechungssignal führt zum Abbrechen des gerade laufenden Programms und zur Fortsetzung der Arbeit des Rechners mit einem anderen Programm. Nach einem Programmunterbrechungssignal wird zunächst eindem Signal zugeordnetes Bedienprogramm abgearbeitet. Erst danach setzt der Rechner das unterbrochene Programm fort. Im einzelnen erzeugt ein Programmunterbrechungssignal folgende Arbeitsgänge:

- Nach Beendigung des gerade laufenden Befehls wird ein INTERRUPT-Zyklus durchlaufen.

- Der Rechner gibt ein Signal „INTERRUPT angenommen“ als Quittung nach außen ab.

- Während des INTERRUPT-Zyklus wird ein INTERRUPT-Befehl gebildet und anschließend sofort abgearbeitet.

Der INTERRUPT-Befehl kann ein Sprung in ein Unterprogramm sein. Das Unterprogramm ist das entsprechende Bedienpro-

gramm. Der Rücksprung ins unterbrochene Programm wird geauso organisiert wie der Rücksprung aus einem Unterprogramm. Am Anfang des Bedienprogramms bringt man im allgemeinen die Inhalte der Register, die nach dem Rücksprung ins unterbrochene Programm noch benötigt werden, in den *STACK* (Stapelspeicher). Vor dem Rücksprung werden die Register wieder mit den im *STACK* geretteten Inhalten gefüllt.

Ein Rechner kann einen oder mehrere INTERRUPT-Eingänge haben. Die zu den Eingängen gebildeten INTERRUPT-Befehle unterscheiden sich. Die einzelnen Eingänge lassen sich im allgemeinen durch spezielle Steuerbefehle sperren und öffnen (sie sind maskierbar). Bei mehreren Eingängen besteht eine Vorrangordnung. Kommen an 2 Eingängen die INTERRUPT-Signale gleichzeitig an, so hat das Signal mit der höheren Priorität den Vorrang. Das andere Signal kann vorgemerkt oder ignoriert werden.

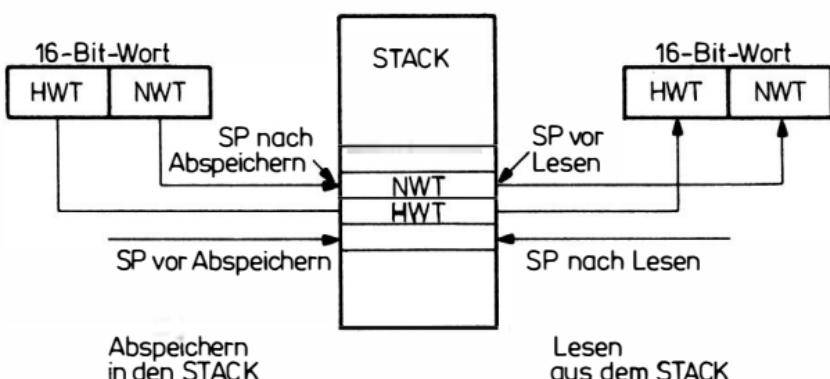

## 2.8. STACK-Organisation

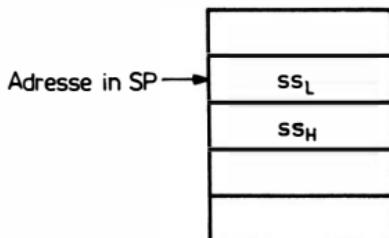

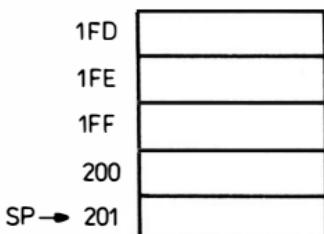

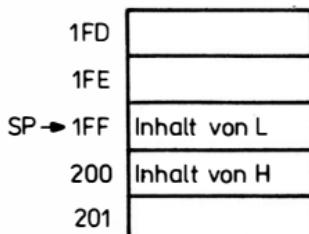

Der *STACK* (auch Stapelspeicher genannt) ist ein Teil des Arbeitsspeichers, der so organisiert wird, wie man Gegenstände in einem Keller ablagert, d. h., die Informationen werden hineingestapelt. Die Information, die zuletzt hineingebracht wurde, muß man auch als erste wieder herausnehmen. Man sagt, die Speicherung geschieht nach dem Prinzip „last in first out“.

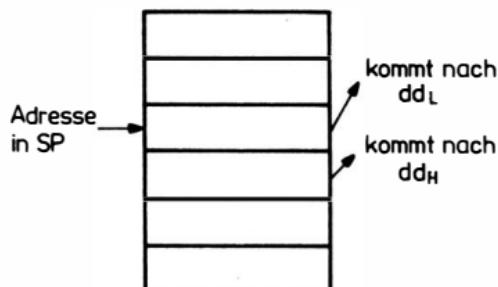

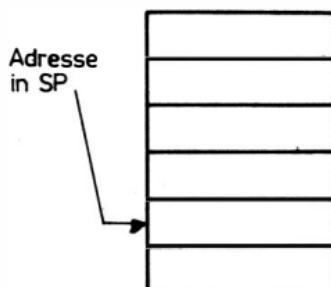

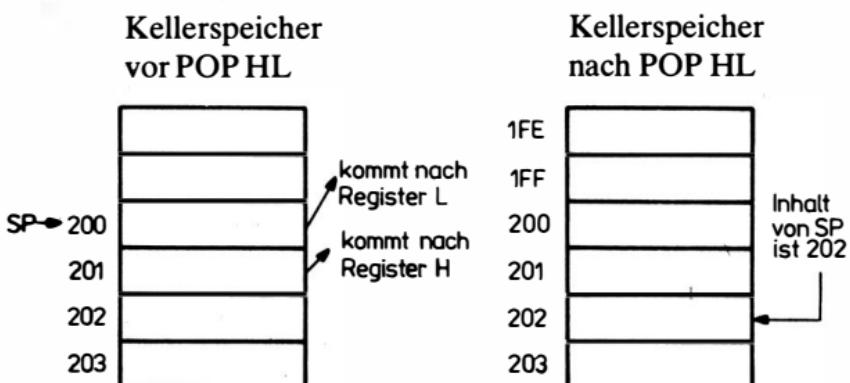

Zur Adressierung des *STACK* dient ein spezielles Register, der *STACKPOINTER* (Stackzeiger). Für die *STACK*-Adressierung gelten im allgemeinen folgende Regeln:

Bild 2.14 Arbeitsweise des *STACK*-Speichers

- Der **STACKPOINTER** (SP) zeigt auf das zuletzt eingeschriebene oder auf das nächste zu lesende Byte.

- Der **STACK** wird von höheren Adressen nach niedrigeren Adressen beschrieben.

- Die Abspeicherung (als **PUSH** bezeichnet) und das Lesen (als **POP** bezeichnet) geschieht meistens mit einem 16-Bit-Wort (2 Byte).

Aus Bild 2.14 ist zu ersehen, in welcher Weise ein 16-Bit-Wort in den **STACK** abgespeichert wird und wie es aus dem **STACK** gelesen wird, wenn eine Speicherzelle 8 Bit (1 Byte) speichern kann.

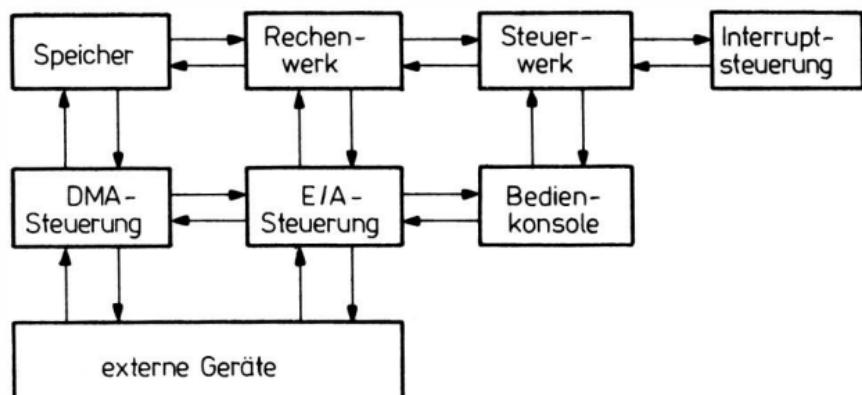

## 2.9. Zusammenstellung der Funktionseinheiten eines Rechners

Aus Bild 2.15 sind die wichtigsten Funktionseinheiten eines Rechners zu ersehen. Für die rein elektronischen Funktionseinheiten (Rechenwerk, Steuerwerk, Speicher, E/A-Steuerung, DMA-Steuerung, INTERRUPT-Steuerung) gibt es spezielle programmierbare Schaltkreise. Dabei werden Rechenwerk und Steuerwerk im Mikroprozessorschaltkreis vereinigt. Für die übrigen Funktionseinheiten gibt es spezielle Schaltkreise.

In Teil 2 sind Grundlagen und Arbeitsweise der programmierbaren Schaltkreise sowie einige Schaltkreise für die genannten Funktionseinheiten eines Rechners beschrieben.

Bild 2.15 Funktionseinheiten eines Rechners

### **3. Aufbau und Arbeitsweise digitaler Schaltkreise für Mikrorechner**

#### **3.1. Übersicht**

Die Digitaltechnik befaßt sich mit der Verarbeitung logischer Signale. Durch die Verfeinerung der Technologie war es im Laufe der Zeit möglich, immer mehr der für diese Verarbeitung notwendigen logischen Grundschaltungen auf einem Chip unterzubringen. Von den ersten SSI-Schaltkreisen, in denen einige Transistoren untergebracht sind, bis zu den LSI-Schaltkreisen mit  $10^4$  bis  $10^5$  Transistoren ging eine intensive technologische Entwicklung parallel.

Während bei den niedrigintegrierten Schaltkreisen das Spektrum von einfachen Grundschaltungen bis zu speziellen Schaltungen wie Zähler, Register, Decoder, Konverter, Multiplexer, Leitungstreiber reicht, geht die Entwicklung der hochintegrierten Schaltkreise in 2 Richtungen. Die eine Richtung ist der spezielle *Kundenschaltkreis*. Dazu gehören z. B. der Taschenrechnerschaltkreis und der Schaltkreis für Digitaluhren. Diese Schaltkreise realisieren eine spezielle Funktion. Die Schaltung ist fest vorgegeben und für die jeweilige Funktion weitestgehend optimal entwickelt.

Die zweite Richtung sind die *programmierbaren Schaltkreise*. Sie sind Bestandteile eines Rechners. Die Entwicklung verläuft zur Zeit in der Richtung, daß einmal die gesamte Zentraleinheit einschließlich der Ein- und Ausgabekanäle auf einem Chip integriert wird. So entstehen heute bereits Chips, die eine minimale Rechnerkonfiguration (CPU, Speicher, Ein-/Ausgabe-Kanäle) realisieren. Die folgende Zusammenstellung zeigt eine Übersicht existierender Schaltkreistypen.

##### *Digitale Grundschatlkreise*

- logische Grundfunktionen

- Flip-Flop-Schaltungen

- Treiber

##### *Analoge Grundschatlkreise*

- Operationsverstärker

- NF-Verstärker

- ZF-Verstärker

- Netzregelschaltkreise

#### *MSI-Schaltkreise der Digitaltechnik*

- Taktgeneratoren

- Codierer und Decodierer

- Register

- Zähler

- Multiplexer

- Rechenschaltungen

- Speicher

- Bustreiber

#### *MSI-Schaltkreise der Analogtechnik*

- Analog-Digital-Umsetzer

- Digital-Analog-Umsetzer

#### *LSI-Kundenschaltkreise*

- Taschenrechnerschaltkreise

- Schaltkreise für Digitaluhren

#### *Programmierbare LSI-Schaltkreise*

(Schaltkreise der Mikrorechentechnik)

- Mikroprozessoren

- Ein-/Ausgabe-Schaltkreise

- INTERRUPT-Schaltkreise

- Schaltkreise zum direkten Speicherzugriff (DMA-Schaltkreise)

## **3.2. Schaltalgebra**

Eine Reihe von Grundfunktionen, z. B. die Entschlüsselung einer Adresse, müssen meistens durch logische Grundschaltkreise aufgebaut werden. Zum Aufstellen solcher Schaltungen ist die Schaltalgebra eine große Hilfe. Sie ist die Grundlage für das Fällen von Entscheidungen und für das Prüfen von logischen Bedingungen. Mit den Binärziffern 0 und 1 werden sogenannte *logische Operationen* durchgeführt. Zu den logischen Operationen gehören:

die ODER-Funktion bzw. Disjunktion (OR),

die UND-Funktion bzw. Konjunktion (AND),

das EXKLUSIV-ODER (XOR)

und die Nicht-Funktion bzw. NEGATION (NOT).

## Die ODER-Funktion

Die ODER-Funktion wird für 2 Binärziffern A und B folgendermaßen definiert:

**Wenn A oder B oder beide gleich 1 sind, so ist das Ergebnis gleich 1. Andernfalls ist das Ergebnis gleich 0.**

Zur Darstellung der ODER-Funktion wird das Symbol „+“ bzw. „ $\vee$ “ (vel – lat., oder) genommen.

Es gelten die Kombinationen:

$$0 \vee 0 = 0,$$

$$0 \vee 1 = 1,$$

$$1 \vee 0 = 1,$$

$$1 \vee 1 = 1.$$

Logische Funktionen werden mit Hilfe einer Funktionstabelle definiert. Die Funktionstabelle enthält die Ausgangssignale, die sich bei den zulässigen Kombinationen der Eingangssignale ergeben. Die Funktionstabelle für die ODER-Funktion ist aus Tabelle 3.1. zu ersehen.

## UND-Funktion

Die UND-Funktion wird für 2 Binärziffern A und B folgendermaßen definiert:

**Wenn A und B beide gleich 1 sind, so ist das Ergebnis gleich 1. Andernfalls ist das Ergebnis 0.**

Zur Darstellung der UND-Funktion wird das Symbol „·“ bzw. „ $\wedge$ “ (et – lat., und) genommen. Es ist auch üblich, daß 2 Binärziffern ohne Operationszeichen aneinandergeschrieben werden:

$$A \cdot B \triangleq A \wedge B \triangleq AB$$

**Tabelle 3.1** Funktionstabelle für die ODER-Funktion

| Eingänge |   | Ausgang    |

|----------|---|------------|

| A        | B | $A \vee B$ |

| 0        | 0 | 0          |

| 0        | 1 | 1          |

| 1        | 0 | 1          |

| 1        | 1 | 1          |

**Tabelle 3.2.** Funktionstabelle für die UND-Funktion

| Eingänge |   | Ausgang      |

|----------|---|--------------|

| A        | B | $A \wedge B$ |

| 0        | 0 | 0            |

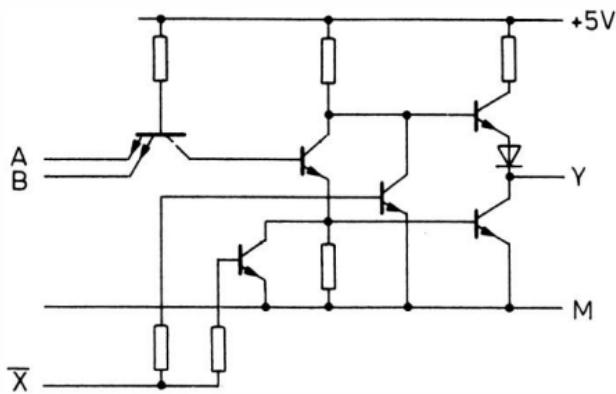

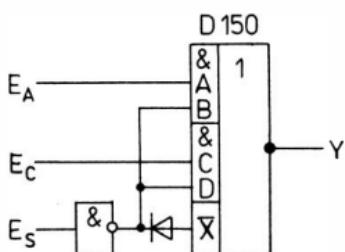

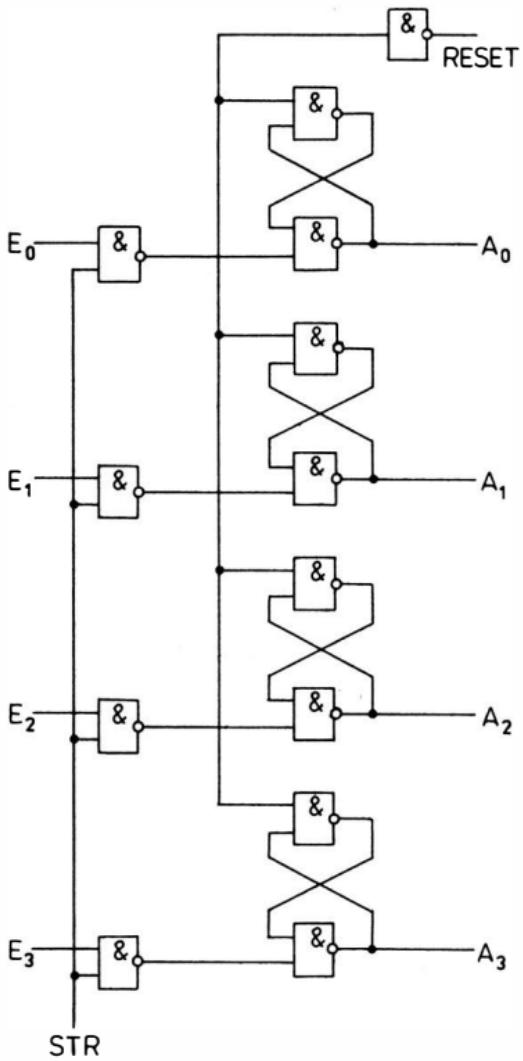

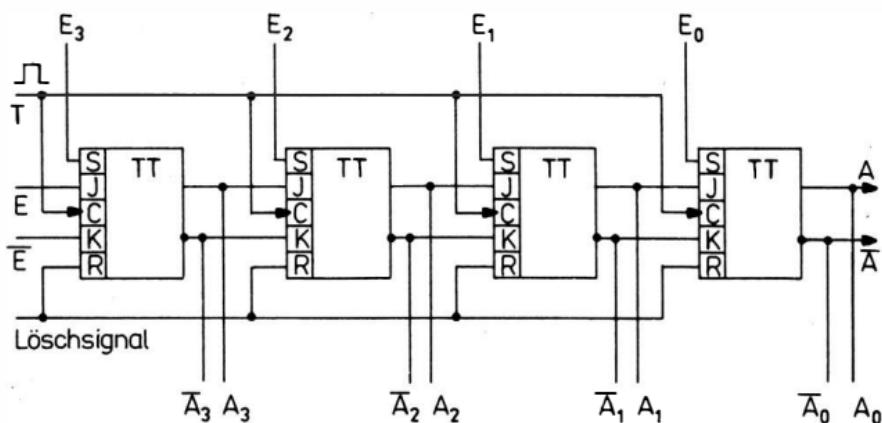

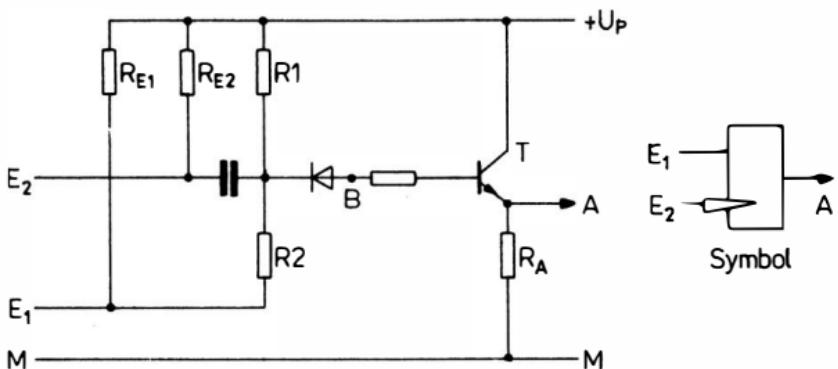

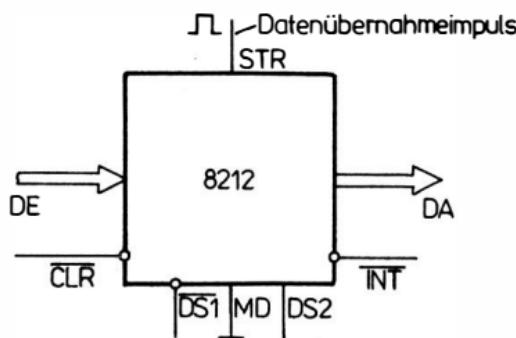

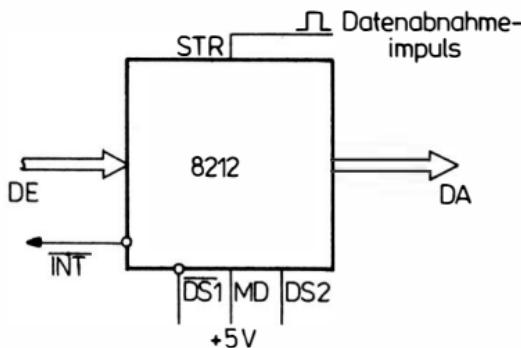

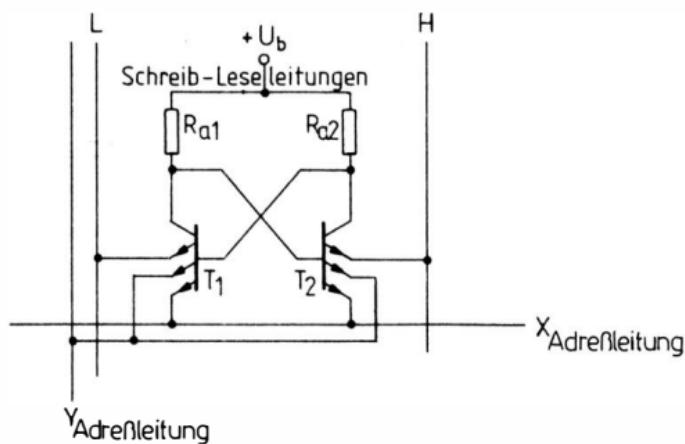

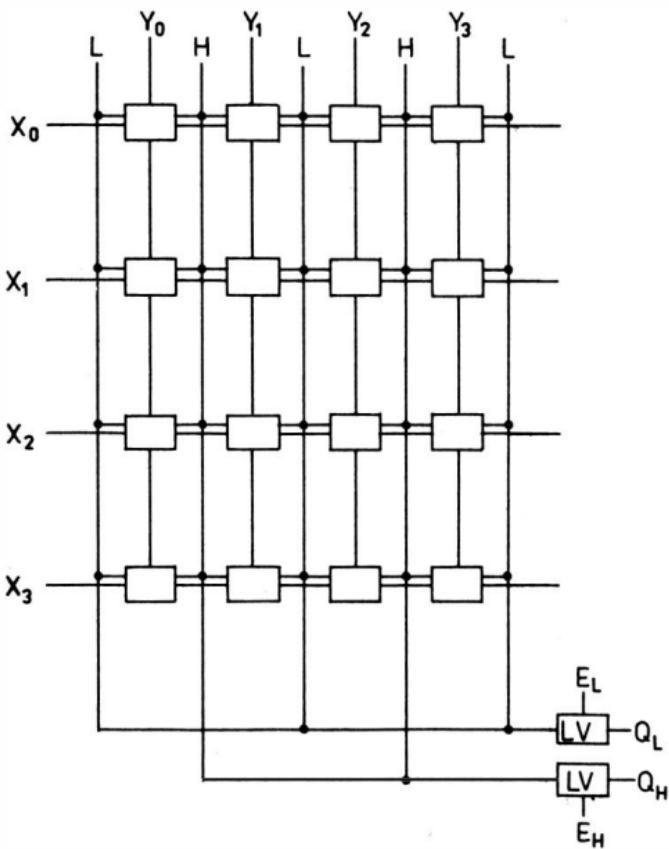

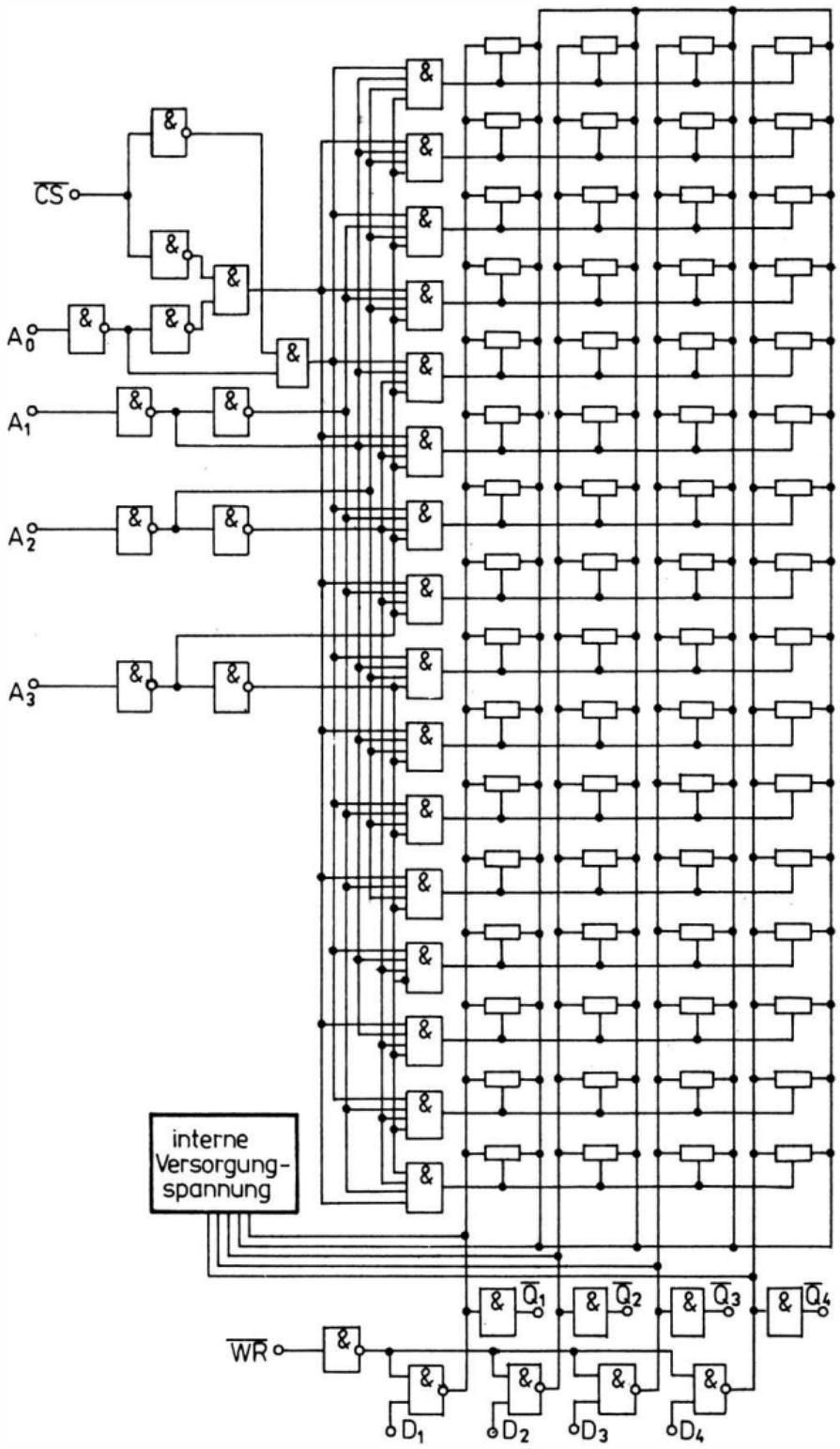

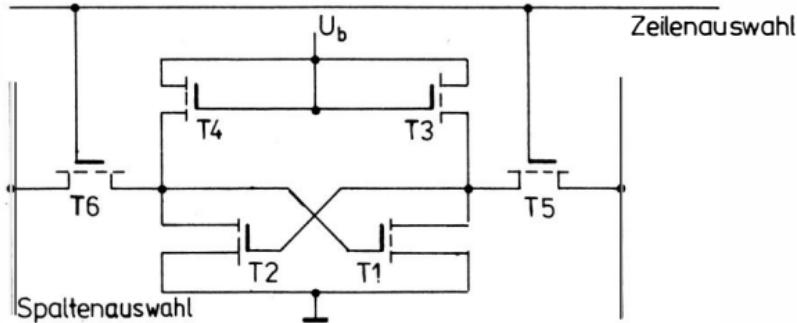

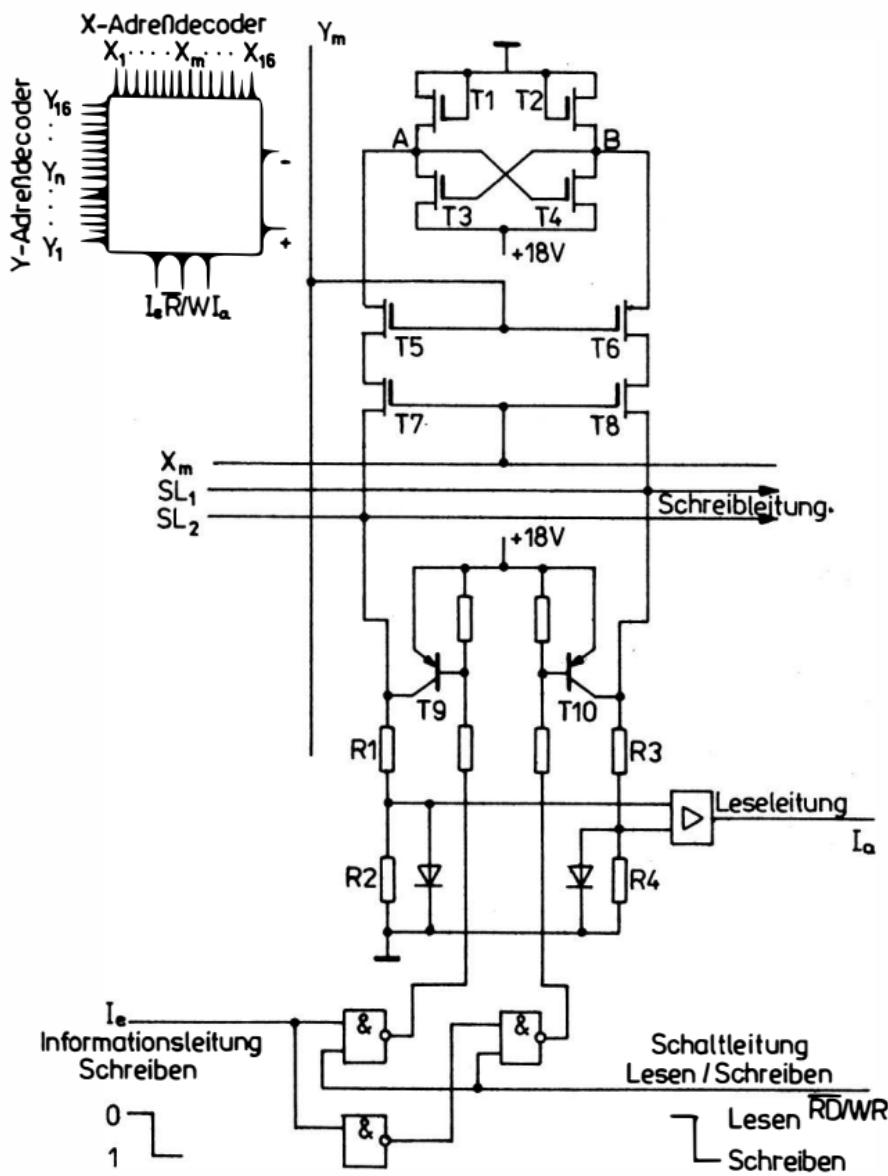

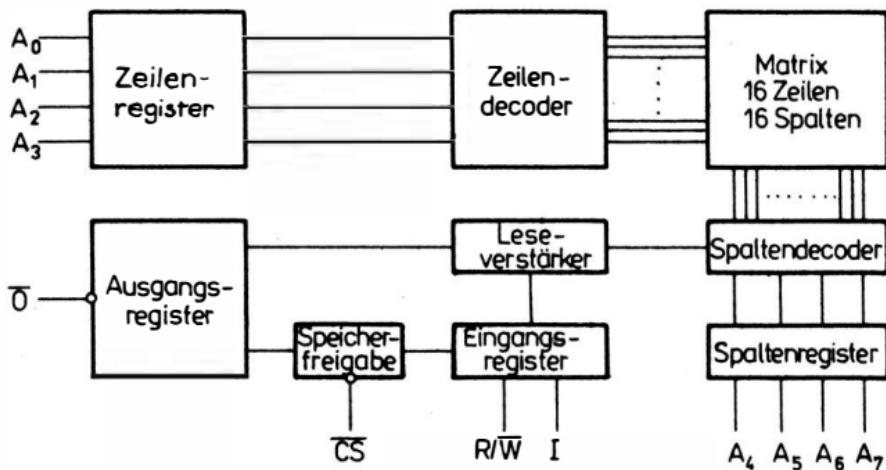

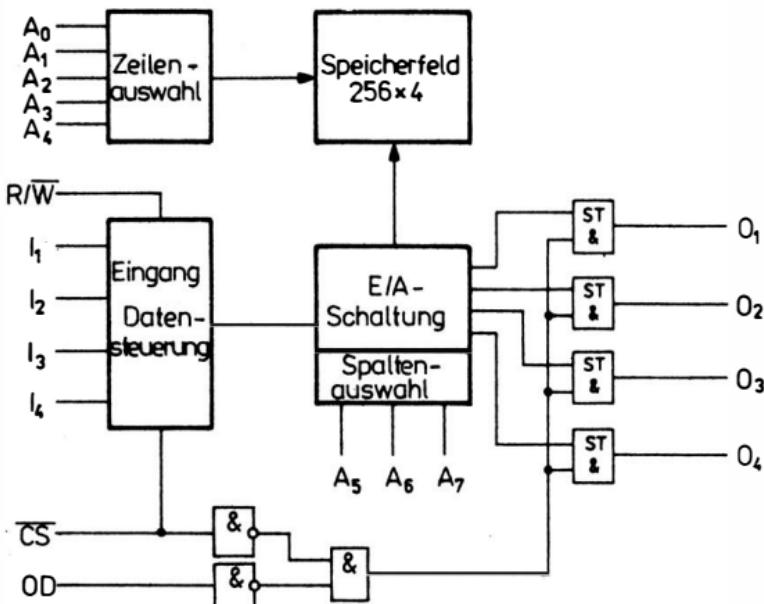

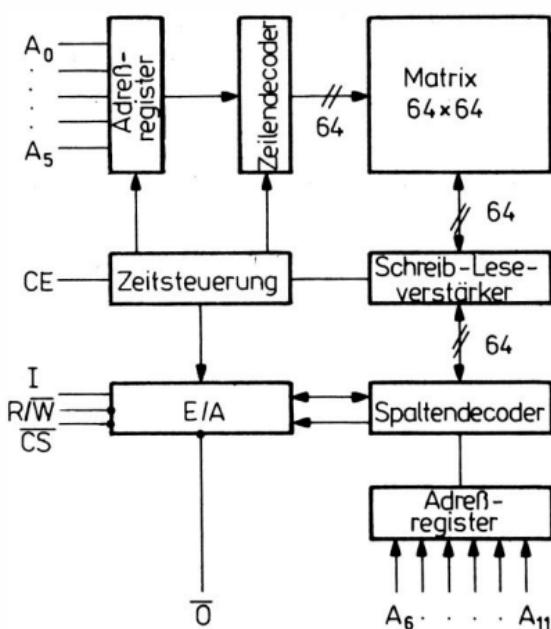

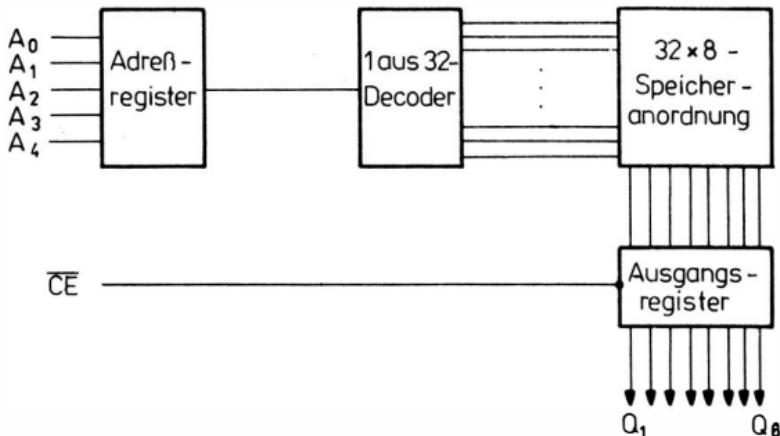

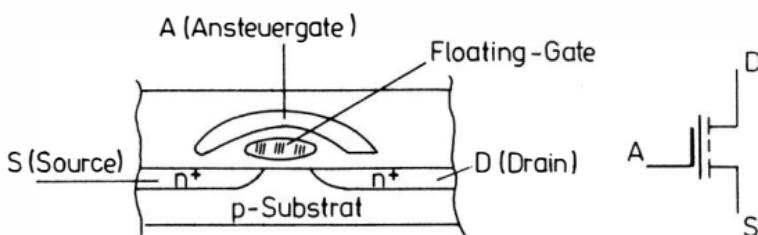

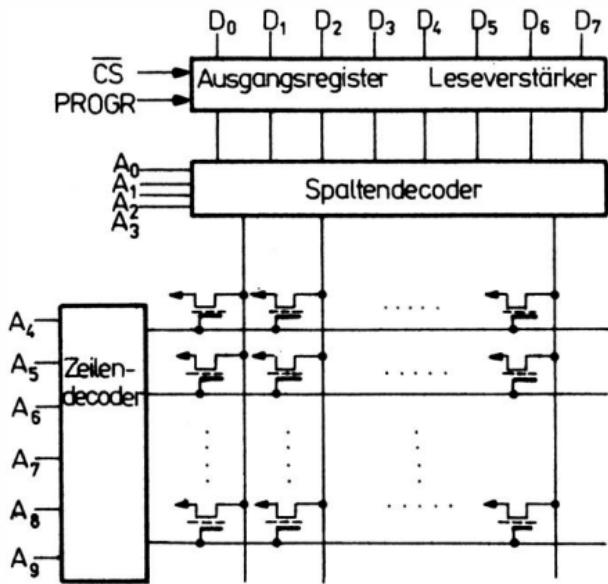

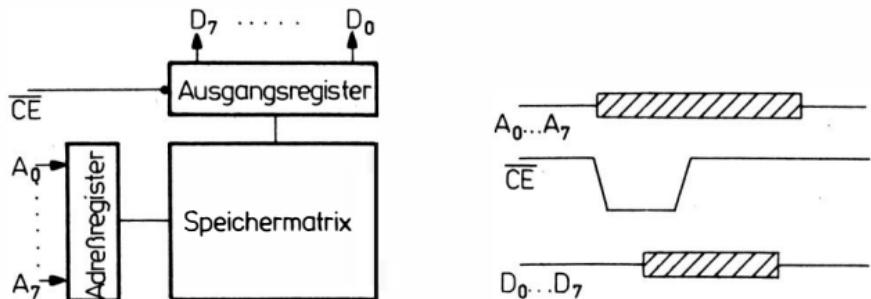

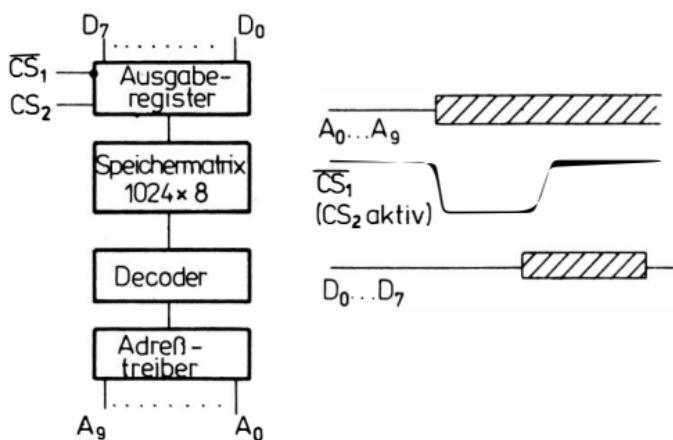

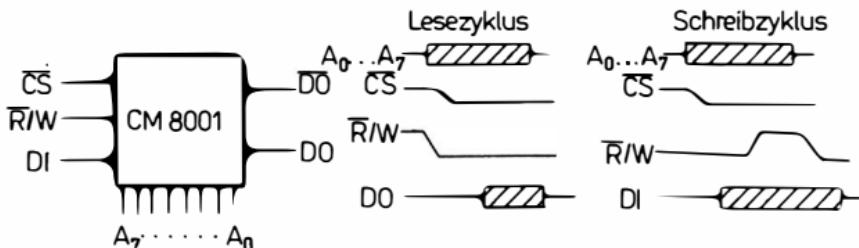

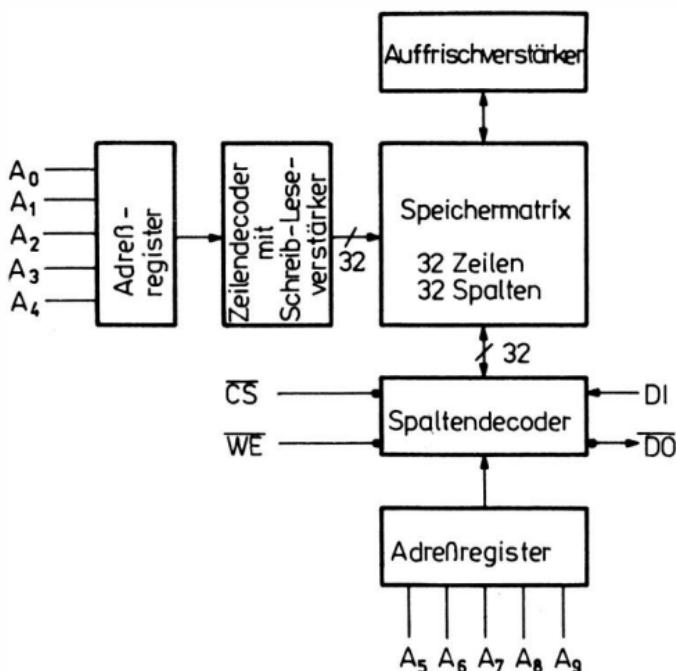

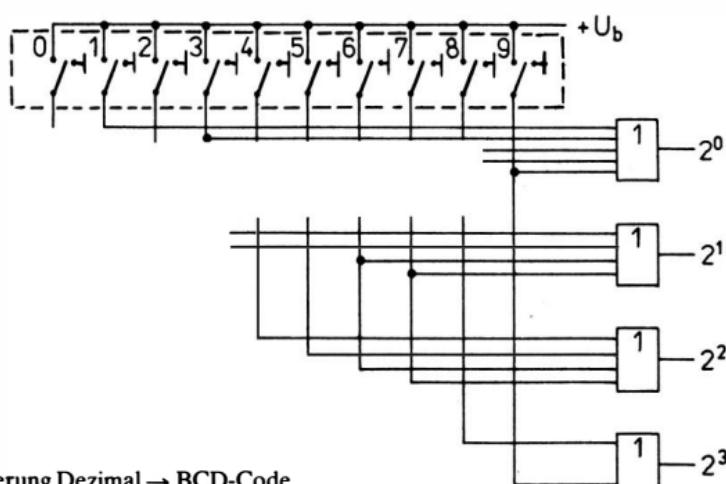

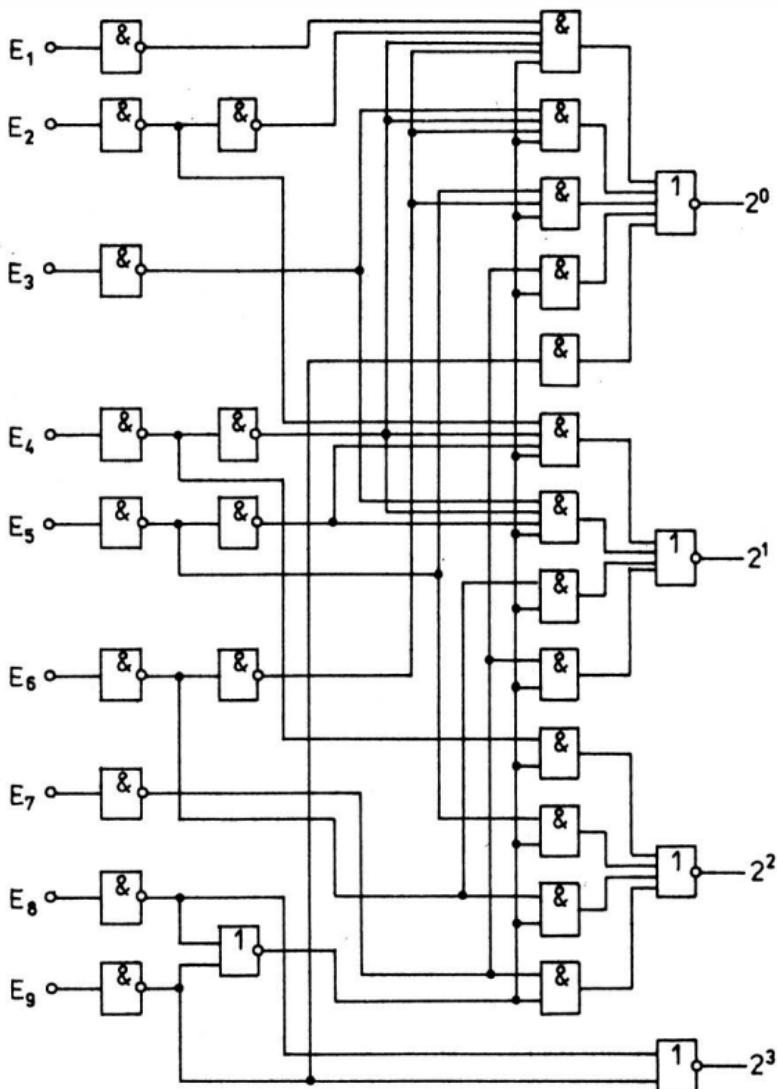

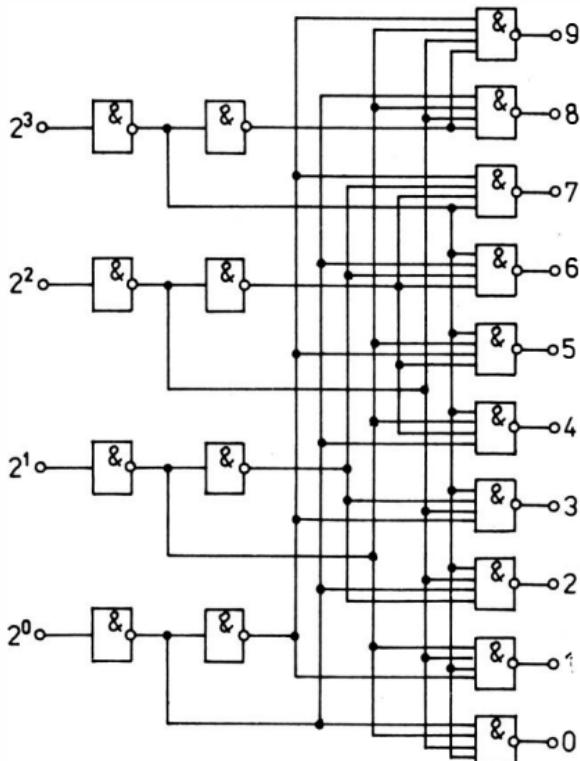

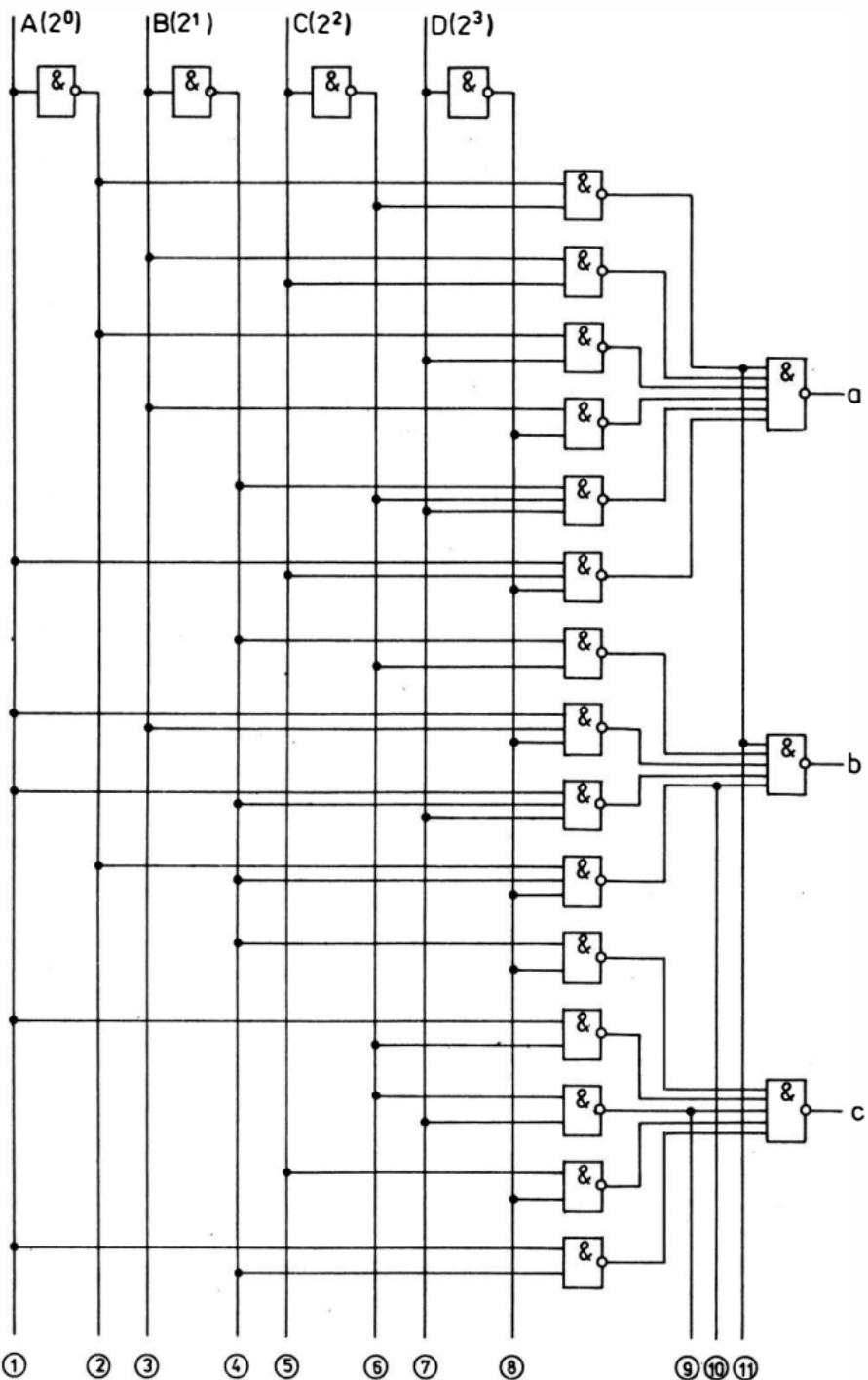

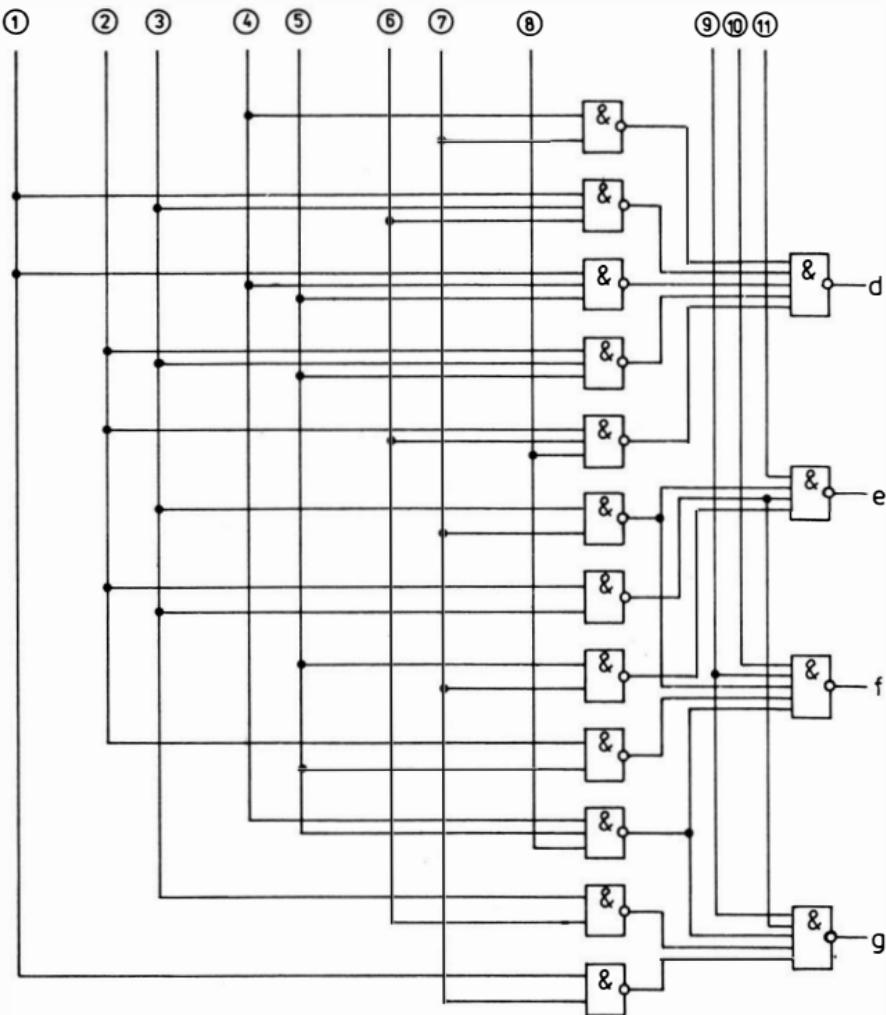

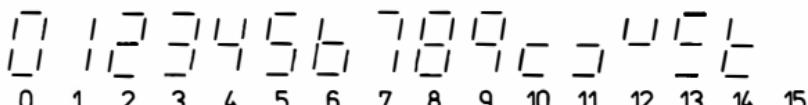

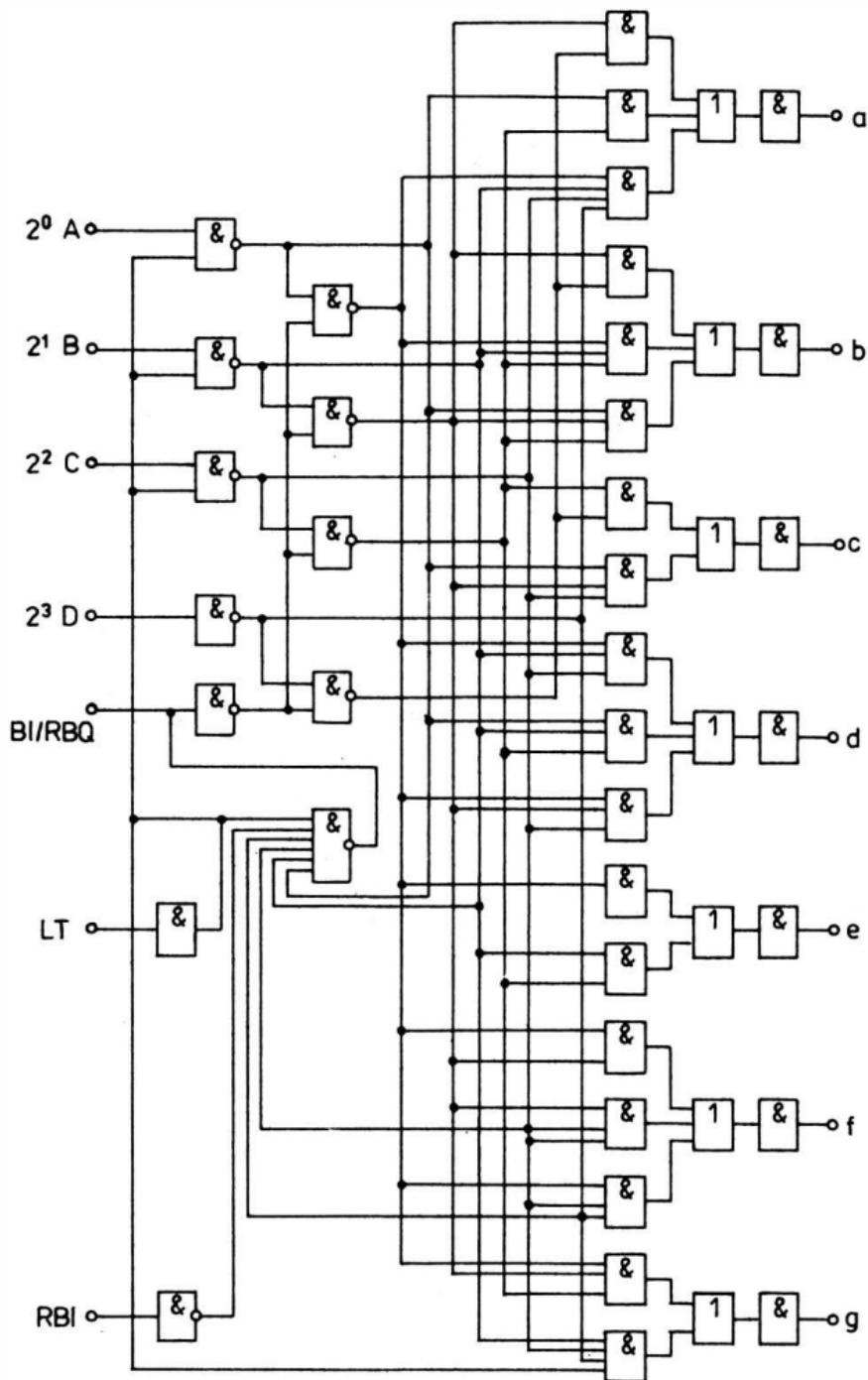

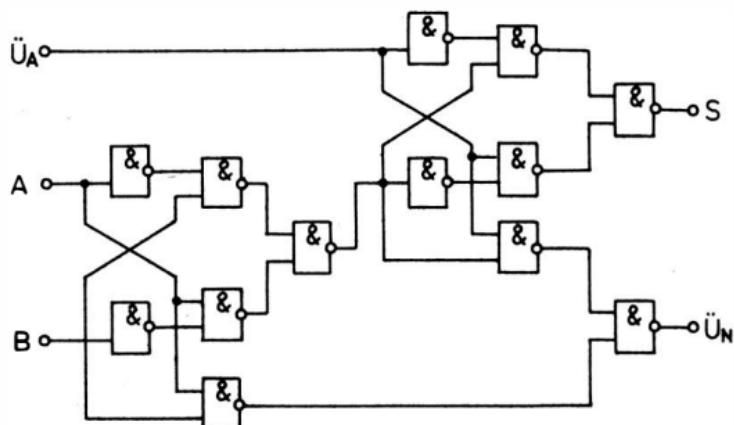

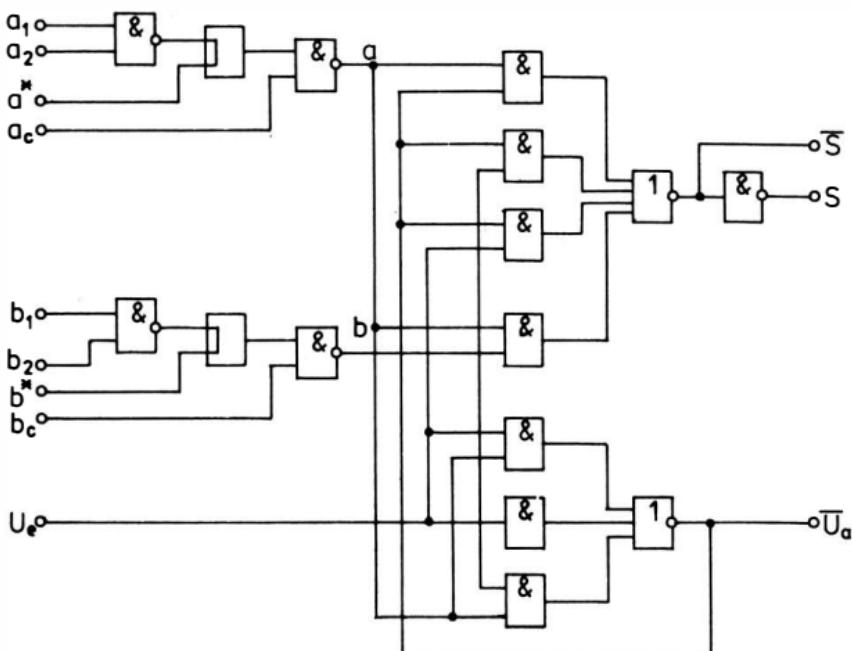

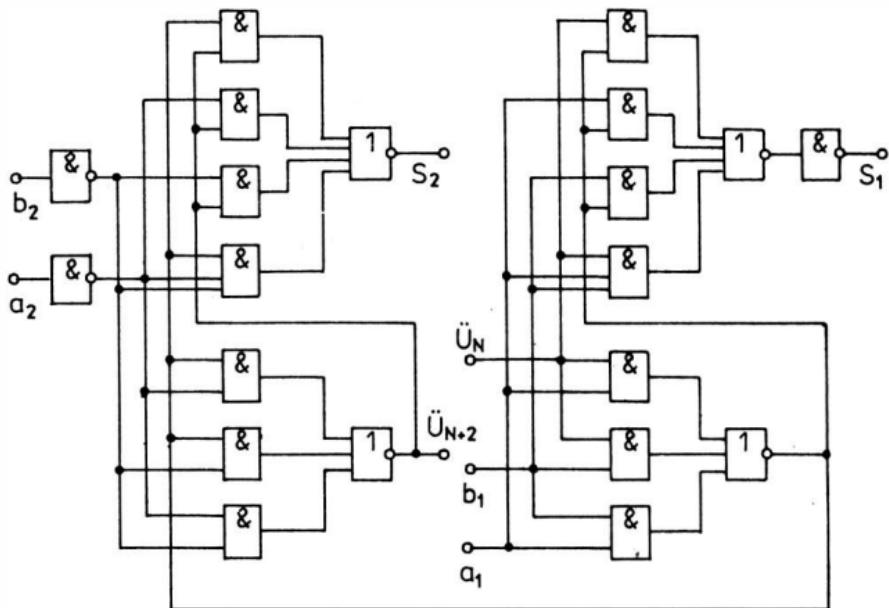

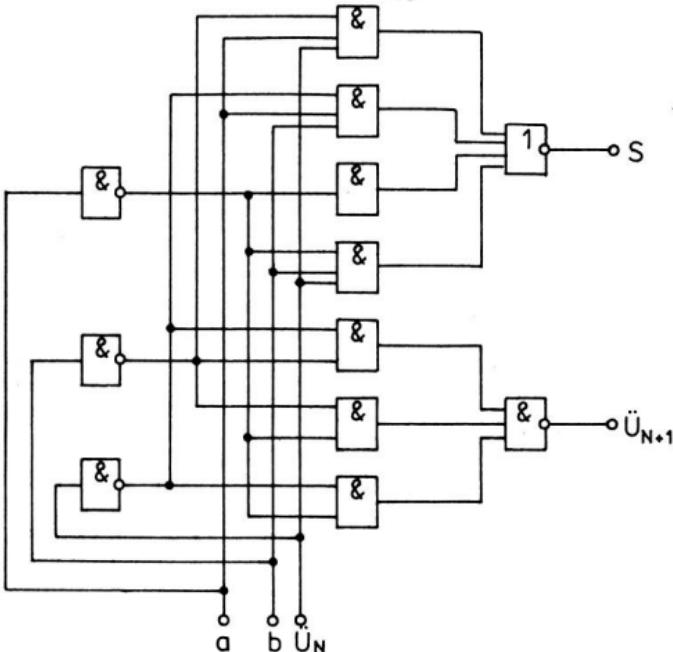

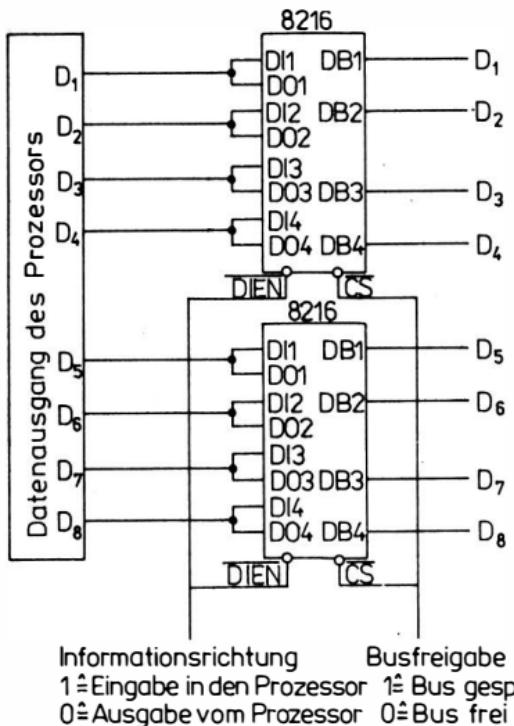

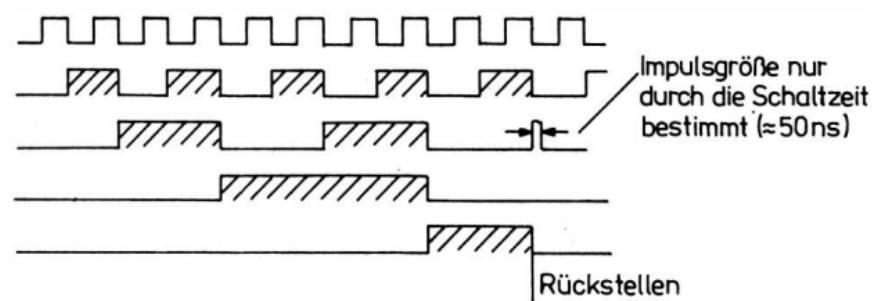

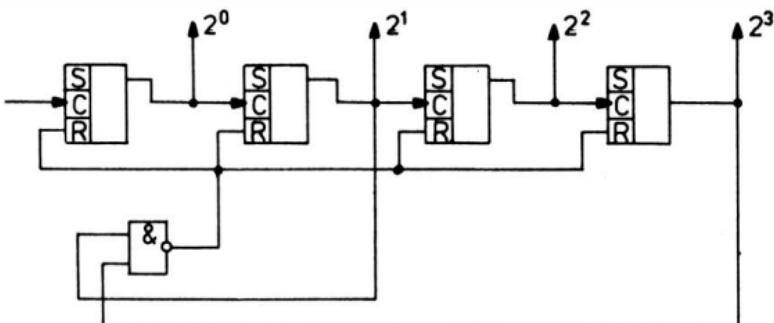

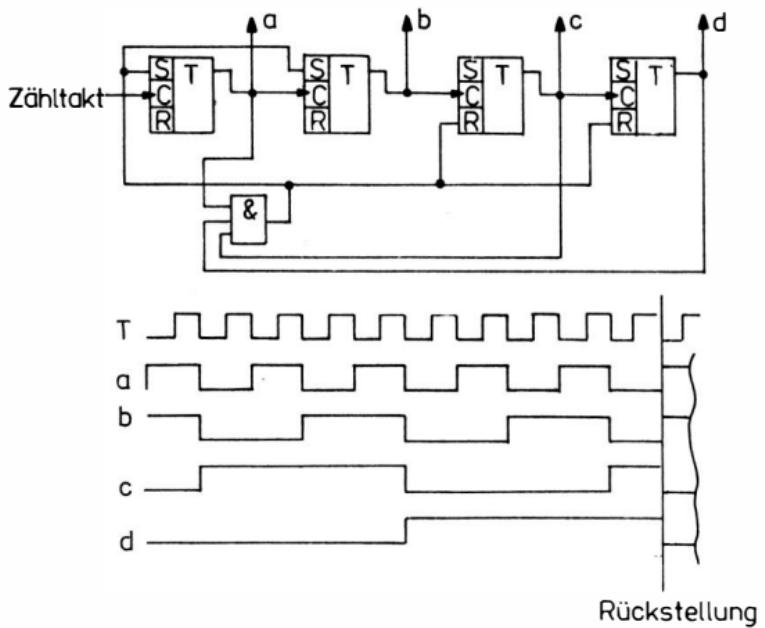

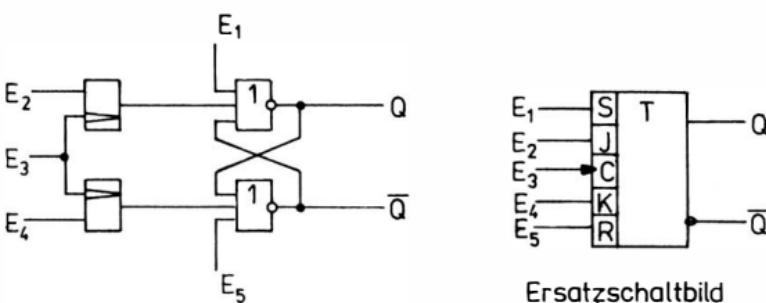

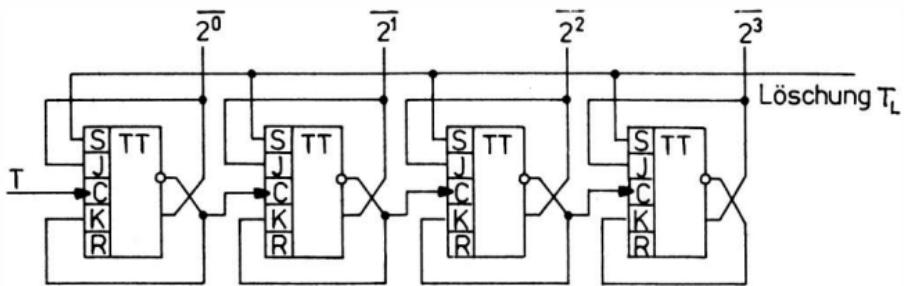

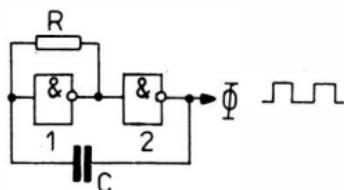

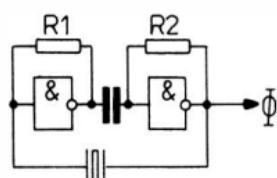

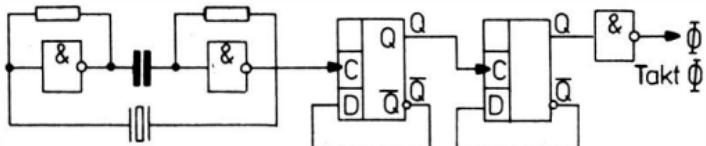

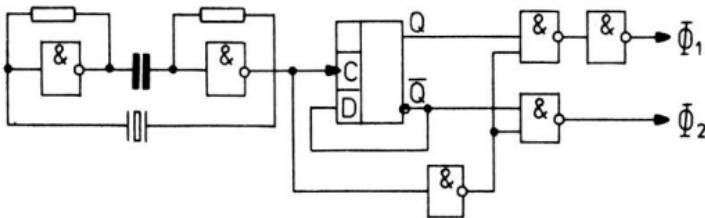

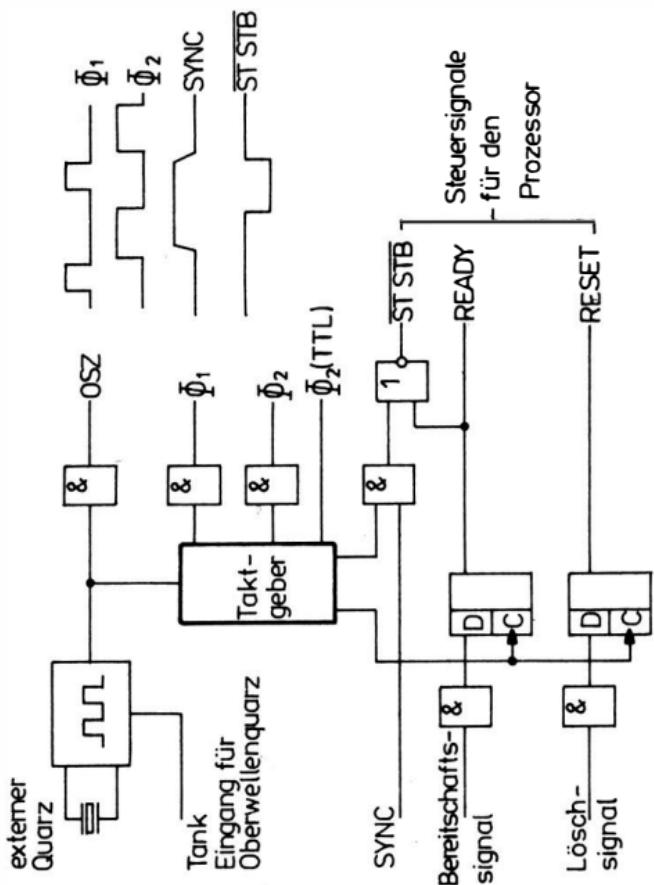

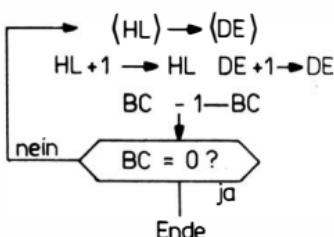

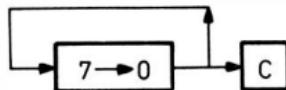

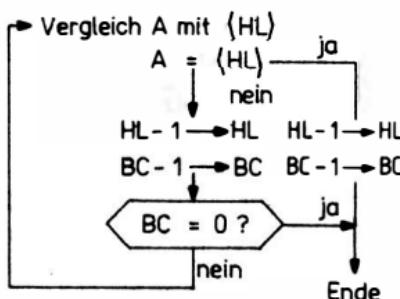

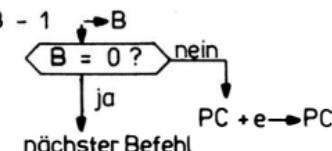

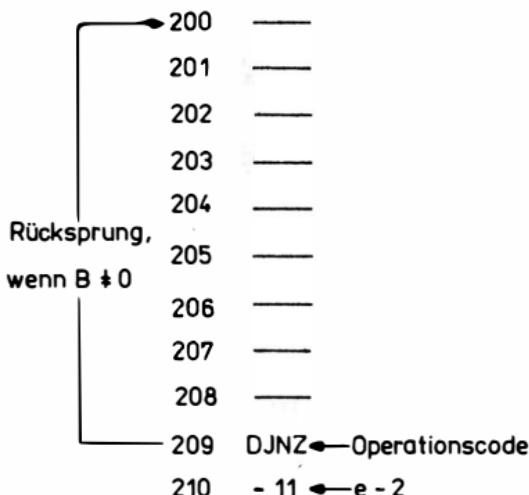

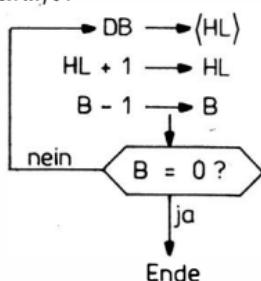

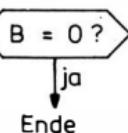

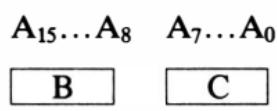

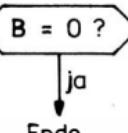

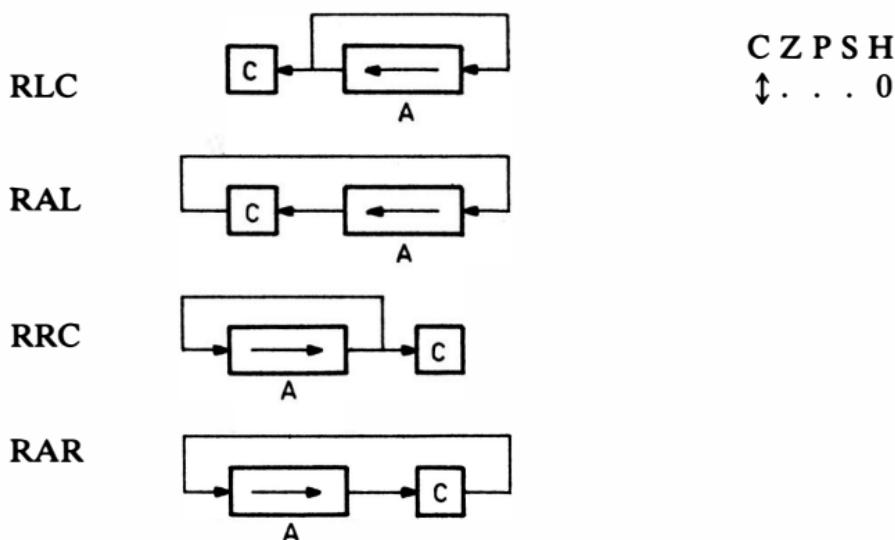

| 0        | 1 | 0            |